DRAMをどう使うか? ――性能の改善技術とその性能を生かす選択方法

●低消費電力化の動向

消費電力の削減は高速化や大容量化とは相反する要素です.しかし,世代交代とともに電源電圧の低下が達成されています.これは「消費電力一定」というユーザの要請にこたえるためのものです(図3).

JEDEC標準DRAMは上記の要請にこたえるものとなっています.JEDEC標準製品の例として0.13μmプロセスを用いた512MビットDDR-I SDRAMを写真1に示します.また,汎用モジュールの大容量化の技術例として,チップを積層するTCP(tape carrier package)を示します(図4,写真2).

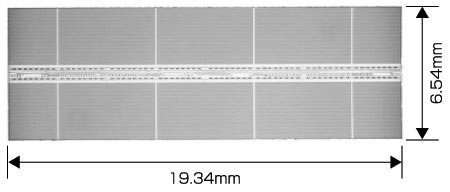

〔写真1〕512MビットDDR-I SDRAM

最新の大容量DRAMの例として,筆者ら(エルピーダメモリ)が開発した512MビットDDR-I SDRAMを示す.設計ルールは0.13μm.すでに量産中である.

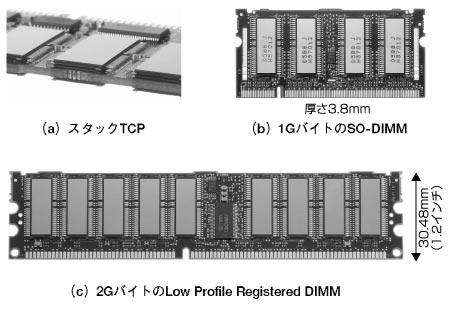

〔図4〕TCPによる高密度実装化

大容量モジュールを実現する手段として,DRAMチップの積層化(スタック)がある.TCP(tape carrier package)はこの目的にかなう技術で,筆者らも製品展開を図っている.図はSO-DIMM(small out-line dual in-line memory module)の断面図である.(a)はTCPを積層して実現した.(b)はTSOP(thin small out-line package)を利用した.

〔写真2〕TCPを用いた高密度DIMM(DDR-Iの例)

TCP技術によって,積層後でも標準品と同じ寸法の大容量メモリ・モジュールを実現できる.ここでは,標準品と同じ厚さにしたSO-DIMMと,高さを抑えたLow Profile Registered DIMMを実例として示す.