プログラマブル・ロジックを集積したSHマイコンのすべて(後編) ――ソフト開発環境とハード開発環境をシームレスにつなぐ

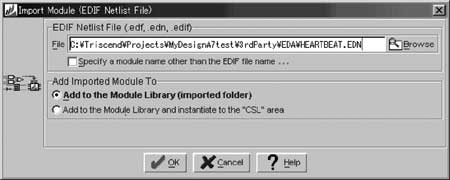

5)EDIFファイルをインポートする

ユーザが自身で論理回路を設計した場合,論理合成ツールや回路図エディタで作成したEDIFネットリストをFastChipに取り込む必要がある.メイン・ウィンドウ上のImportボタンを押すと,EDIFファイルを読み込むためのダイアログ・ボックスが現れる(図9).EDIFファイルを取り込むと,それに対応するアイコンがIPモジュール・ライブラリの枠内に表示される.これをCSLの枠にドラッグ・アンド・ドロップすれば,CSLに組み込まれる.

〔図9〕EDIFファイルのインポート

論理合成ツールや回路図エディタで作成したEDIFネットリストをFastChipに取り込む場合,メイン・ウィンドウのImportボタンを押してこのダイアログ・ボックスを開く.取り込んだ回路は,IPモジュール・ライブラリのリストに表示される.

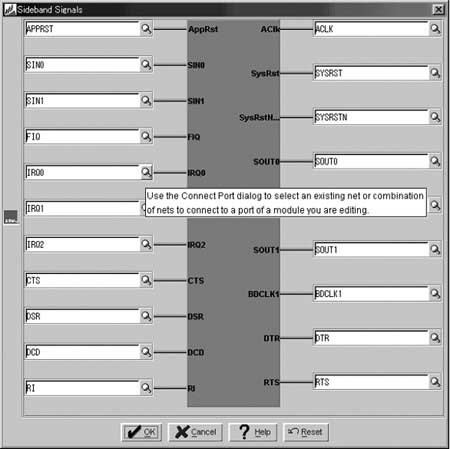

6)サイドバンド信号を割り当てる

CSLには,バス以外の内部信号を接続することもできる.メイン・ウィンドウのMCUボタンを押すと,CSLの外部信号や入出力信号とどの信号を接続するかを選択するためのダイアログ・ボックスが現れる(図10).

〔図10〕サイドバンド信号の設定

真ん中の縦長の箱がCPUに相当する.CPUバス以外の信号は,CSLの内部信号や入出力信号と接続できる.