東芝製コンフィギャラブル・プロセッサの開発環境が一堂に ――MeP World 2004

2004年8月26日,「MeP(Media Embedded Processor)World 2004」が東京国際フォーラムにて開催された(写真1).2004年6月に,日米欧のソフトウェア開発ツール・ベンダ,EDAベンダ,設計会社,IPベンダ12社が,東芝製の32ビット・コンフィギャラブル・プロセッサ・コア「MeP」を搭載するシステムLSI設計やソフトウェア開発について,共同マーケティングを実施することで合意している.MeP World 2004では,この12社および東芝による製品の展示とセミナが行われた.MePに対応した評価ボードやソフトウェア開発ツール,ハードウェア/ソフトウェア協調検証環境などのデモンストレーションや展示が行われた.

MePは,アプリケーションに応じてカスタム命令を追加したり,DSP(digital signal processing)回路や専用ハードウェア・アクセラレータ回路などの拡張機能を追加することが容易,という特徴がある.MePのアーキテクチャは三つの階層からなる(図1).すなわち,コンフィギャラブル・プロセッサ・コアの「MePコア」,MePコアと拡張機能やローカル・バスで構成される「MePモジュール」,MePモジュールを組み込んだLSI「MeP SoC」である.

[写真1] MeP World 2004

MeP World 2004は,共同マーケティングに合意した日米欧のソフトウェア開発ツール・ベンダ(アドバンスド データ コントロールズ,ソフィアシステムズ,レッドハット),EDAベンダ(インターデザイン・テクノロジー,パシフィック・デザイン,日本セロックシカ,コーウェア,日本シノプシス),設計会社(沖ネットワークエルエスアイ,シーデックス,大日本印刷),IPベンダ(ソニックス)の12社の共催として開催された.

[図1] MePアーキテクチャの概略

MePコア,MePモジュール,MeP SoCの三つの階層からなる.

●MePコア用評価ボードのデモンストレーションを実施

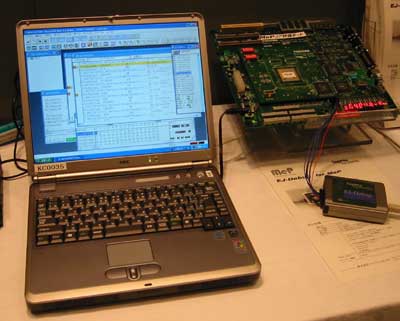

ソフィアシステムズは,MePコア評価ボードとデバッガ「EJ-Debug for MeP」のデモンストレーションを行った(写真2).

本評価ボードは,FPGAボード「BDS006 EVA BOARD/MeP CORE」とメイン・ボード「BDS004 MeP EVA BOARD/MAIN」からなる.FPGAボードは,MePコアの回路を実装した米国Altera社のFPGA「Stratix(EP1S40F1020C7)」や128MビットSDRAM,JTAGコネクタ,2チャネルのシリアル・インターフェースなどを搭載している(写真3).外形寸法は150mm×200mm.メイン・ボードは,2Mバイトのフラッシュ・メモリ,2チャネルのシリアル・インターフェース,1チャネルのパラレル・インターフェースなどを備えている.外形寸法は300mm×270mm.

デモンストレーションでは,評価データのメモリやレジスタの内容を確認したり,逆アセンブルなどを本デバッガ用ソフトウェア「WATCHPOINT」を用いて行った.

評価を行うにあたっては,このほかに同社のエミュレータ「UniSTAC II/J for MeP」やAltera社のFPGA/CPLD開発ツール「Quatus II」,米国RedHat社のMeP用開発ツール「GNUPro for MEP」などが必要である.GNUPro for MePは,MePコアのコンフィグレーションに合わせて,コンパイラ(gcc)やシミュレータ(sid),デバッガ(gdb)などのソフトウェア開発ツールを自動生成する.

[写真2] ソフィアシステムズのデモンストレーション

MePコア評価ボードとデバッガ「EJ-Debug for MeP」を用いて実機による性能評価を行う.本製品の出荷はすでに始まっている.

[写真3] MePコア評価ボード

BDS006は,MePコアを実装したFPGA(米国Altera社のEP1S40F1020C7)や128MビットSDRAM,JTAGコネクタなどを搭載している.メイン・ボード「BDS004 MeP EVA BOARD/MAIN」と組み合わせて利用する.

本評価ボードに実装されているMePコアのコンフィグレーション・データは,沖ネットワークエルエスアイが開発した.現在提供されているMeP-c2コアのほか,SDRAMコントローラ,UARTを内蔵している.また,オン・チップ・バスはAMBA(Advanced Microcontroller Bus Architecture)のAHB(Advanced High-performance Bus)を採用している.動作周波数は20MHz.

MePコアでは,オプション命令(32ビット乗算・除算命令,ビット操作命令など)やメモリ構成(命令/データ・キャッシュ容量,命令/データRAM容量),割り込みコントローラ,タイマなどの有無について,アプリケーションに合ったコンフィグレーション(構成)を選択できる.本評価ボードに実装されているMePコアの場合,8Kバイトの命令キャッシュ,16Kバイトのデータ・キャッシュ,32バイトの命令RAM,128KバイトのデータRAMのメモリ構成となっている.また,タイヤや割り込みコントローラを備えている.

MePコアを別の構成にしたり,周辺回路を追加したい場合,沖ネットワークエルエスアイがカスタマイズを行う.同社のブースでは,カスタマイズ例として,音声CODECのAC97用コントローラを追加したコンフィグレーションのボードを用いてデモンストレーションを行っていた(写真4).

[写真4] 沖ネットワークエルエスアイのデモンストレーション

デモンストレーションでは,評価ボードのメイン・ボードに実装したAC97 CODECの機能を利用して音声出力を行っていた.コア・データ(FPGAのコンフィグレーション・データ)にAC97コントローラを追加した.

アドバンスドデータコントロールズは,MePに対応した米国Green Hills Software社のソフトウェア開発環境「MULTI for MeP」を展示した(写真5).MePを利用したシステムLSI(MeP SoC)に実装するアプリケーション・ソフトウェアを開発する際に用いる.

前述のように,RedHat社の「GNUPro for MeP」がコンフィグレーションに合ったコンパイラ(gcc)を生成し,このコンパイラによって作成された実行ファイルを東芝製のソフトウェア・シミュレータやsidでシミュレーションする.これらのツールは,MULTIのGUIを用いて起動したり操作できる.また,ソフィアシステムズのICE(in-circuit emulator)「UniSTAC II/J」と接続することで,実機によるデバッグを行える.

MULTIのバージョンはv4.0に対応している.GNUPro for MePについては,ユーザが別途用意する必要がある.

[写真5] MULTI for MePのデモンストレーション

MULTIのバージョンはv4.0に対応している.GNUPro for MePについては,ユーザが別途用意する必要がある.本ソフトウェア開発環境の発売時期は未定.

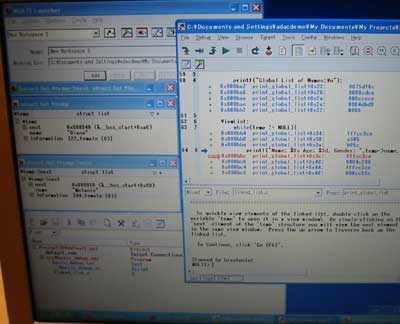

●MePハードウェアとソフトウェアの協調開発環境

インターデザイン・テクノロジーは,MePを利用したシステムLSI(MeP SoC)用の統合開発環境「VisualSpec/MeP協調設計スイート」のデモンストレーションを行った(写真6).本開発環境は,同社のC言語ベースのシステム・レベル設計環境「VisualSpec ver2.0」とRedHat社のMeP用ソフトウェア開発環境「GNUPro for MeP」を統合したものである.

MePコアで実行するソフトウェアの中に要求性能を満たさない処理がある場合,その処理をMePの追加機能の一つである専用ハードウェア・アクセラレータ回路(ハードウェア・エンジンと呼ぶ)として実装することで,問題となる処理性能を引き上げる.VisualSpecは,ハードウェア・エンジンの各機能アルゴリズムをC言語で記述してモデリングを行ったり,デバッグを行う.VisualSpecとGNUPro for MePのシミュレータを協調動作させることが可能なため,ハードウェア・エンジンとソフトウェアの協調検証を行える.

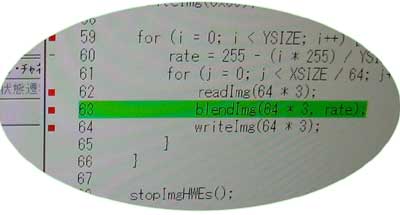

デモンストレーションでは,二つの画像のアルファ・ブレンディング(半透明な画像と別の画像を重ね合わせる処理)を行うMePモジュールのデバッグを行った.このMePモジュールでは,画像の読み出しはソフトウェアで行い,その画像を合成する処理はハードウェア・エンジンで行っていた.

(a) 「VisualSpec/MeP協調設計スイート」:手前の画面がGNUProfor MeP,奥の画面がVisualSpec

(b) GNUPro for MePの画面:緑色のライン(画像を合成する処理)は,ハードウェアで処理する.

(c) VisualSpecの画面:(b)のGNUPro for MePから移動したところ.画像合成の処理を行っている.

[写真6] インターデザイン・テクノロジーのデモンストレーション

アルファ・ブレンディングを実行するMePモジュールのデバッグ.ハードウェア・エンジンが処理を開始する位置にブレーク・ポイントを設定した.ソフトウェアで画像読み出しを行った後,処理の主体がハードウェア・エンジンに移っているかどうか,その処理が終わった後,ソフトウェアに戻っているかどうかなどをチェックしていた.

●MePを利用したシステムLSIの開発フロー

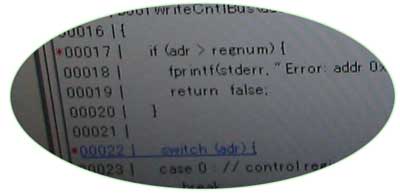

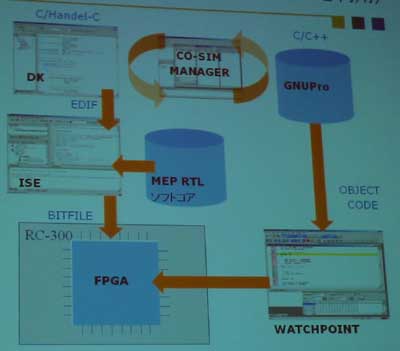

日本セロックシカは,同社のC言語入力の論理合成ツール「DK design suite」を用いたMeP SoCの開発について講演を行った(写真7).本ツールを利用した開発工程は大きく二つに分かれている.一つはFPGAにMePのソフト・マクロ(RTLソース・コード)を実装して動作確認を行うプロトタイプの工程であり,もう一つは動作確認済みのコンフィグレーション・データを用いてASICを開発する工程である.

プロトタイプ開発では,C/Hanel-Cなどで記述したハードウェア・モデルをDK design suiteでシミュレーションした後,生成したネットリスト(EDIF)をFPGA用配置配線ツール(米国Xilinx社のISE)に渡し,FPGA(Xilinx社のVirtex-II)に実装する.FPGAボードは,同社が出荷している「RC300プロトタイピング開発プラットフォーム」を利用する(写真8).また,RedHat社のGNUPro for MePと連携して利用できる.

ASICの開発において,ネットリストの作成にはDK design suiteを利用する.なお,評価ボードは現在開発中である.

[写真7] プロトタイプの開発フロー

日本セロックシカは,同社のDK design suiteを利用したMeP SoC開発フローについて講演を行った.

[写真8] RC300を利用した開発プラットホーム

RC300の評価ボード.今後,本ボードを利用してMePコアの評価を行う予定.本ボードは,Xilinx社のFPGA「Virtex-II(XC2V6000)」,32MバイトSRAM,USBインターフェースなどを搭載している.