プログラマブル・ロジックを集積したSHマイコンのすべて(後編) ――ソフト開発環境とハード開発環境をシームレスにつなぐ

●ハード環境とソフト環境の両方を含むFastChip

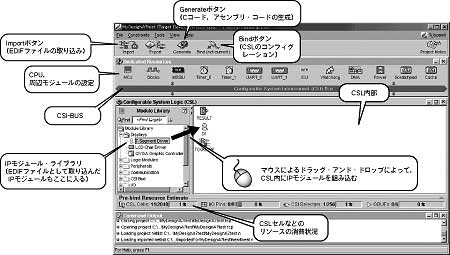

CSoC開発環境の中核となるのは,Triscend社が用意するFastChipである(図3).ここではFastChipの概要について説明する.

まず,プログラマブル・ロジックの開発環境について,FastChipは2通りの方法を提供する.一つ目の方法は,あらかじめFastChipが用意している各種のIPモジュールを用いる方法である.この場合,ユーザはFastChipの画面上でマウスをドラッグ・アンド・ドロップするだけで,所望のIPモジュールをプログラマブル・ロジック(CSL)に組み込むことができる.

二つ目の方法は,ユーザ自身がプログラマブル・ロジックに実装する論理回路を設計する方法である.これは通常のFPGA/PLD開発と同じである.まず,Verilog HDLやVHDLなどのハードウェア記述言語で論理機能を記述し,論理合成ツールを用いてEDIF(Electronic Design Interchange Format)ネットリストを生成する.または,回路図エディタを利用してEDIFネットリストを作成する.これらの論理合成ツールや回路図エディタは,FPGA/PLD向け設計ツールを出荷している著名なEDAベンダから提供される予定である.また,ユーザが設計した論理回路をシミュレーションできるように,CSLにつながるCSI-BUS(Configurable System Interconnect BUS)のバス・トランザクション・モデルなども提供される.

FastChipは,ユーザが選択したIPモジュールや,ユーザが開発したEDIFネットリストの情報を基に配置配線を行い,コンフィグレーション用データ・ストリームを生成する.前編で説明したように,このデータ・ストリームは通常ROMに格納され,CPUの命令またはDMA(direct memory access)コントローラによってCSLのコンフィグレーション・メモリに転送される.

FastChipでは,このコンフィグレーション時にマッピング後の論理回路のタイミングを検証する.すなわち,静的タイミング解析(STA:static timing analysis)のレポート結果を出力する.

また,FastChipは同時に,CPUからアクセスするCSL内のレジスタ群のアドレスを自動的に割り当てる.さらに,Cコンパイラまたはアセンブラのヘッダ・ファイルとして利用できるアドレス・マッピングの定義ファイルを生成したり,チップ内の機能設定レジスタの設定ルーチン・プログラムを生成する.こうして,ハードウェアとソフトウェアの間をシームレスにリンクできるようになっている.

〔図3〕FastChipのメイン・ウィンドウ

Windows上で動作する.CSLに実装するハードウェアとCPU上で動作するソフトウェアの両方の開発に対応している.ここではTriscend社のA7シリーズ(内蔵CPUはARM7TDMI)の画面を掲載する.現在開発中のSH対応版でも,一部変更はあるが,基本的に同じ画面になる.