大容量ストレージを使いやすくするUSB 3.0 ――使い慣れたUSBの転送速度が5Gbpsに向上

●下位互換を維持するため,バス構造は複雑

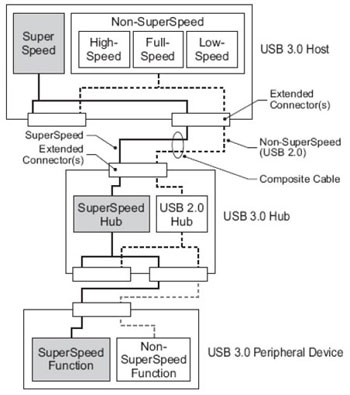

図2はUSB 3.0のバス・アーキテクチャを示しています.下位互換を維持するために「デュアルバス・アーキテクチャ」が採用されており,電気的にも機械的にも上位および下位互換として設計されています.USBデバイスの検出とシステム構成時は,最速の転送レートにて行われます.つまり,USB 2.0下位互換なので,Low SpeedデバイスはLow Speedにてデバイス検出とバス・エヌマレーションが行われ,Full SpeedデバイスはFull Speedにてデバイス検出とバス・エヌマレーションが行われます.また,ハブはその性格上,追加の接続点を提供します.

図2 USB 3.0のバス・アーキテクチャ

SuperSpeed USBでは以下の方式が採用されています.

- 2線式単信方式の信号伝送

- パケットがデバイスへ決まったルートを経て送られる

- ハブはデータを蓄積して送り出す

- 非同期通知(Asynchronous Notifications)

1) 階層アーキテクチャ

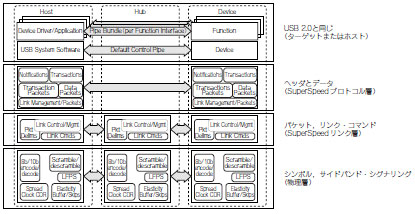

図3を見てください.この図はUSB 3.0の階層アーキテクチャを端的に説明しています.最下層の物理層から最上位層のプロトコル層まで,大きく四つに分けて説明されます.