PLD デバイス・アーキテクトの決断 ――Altera社 ARM-based Excalibur の場合

PLDベースのシステムが急増する中,エンジニアはディスクリート部品とPLDを組み合わせたり,PLDやASICにIPコアを実装するなど,さまざまな設計手法を利用しています.

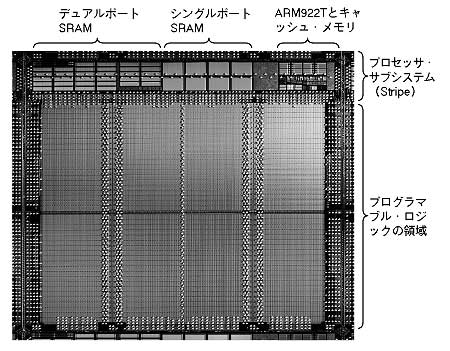

2001年の夏,筆者ら(米国Altera社)はハード・マクロのCPUコアを内蔵したPLD「ARM-based Excalibur(EPXA)ファミリ」を出荷しました(表1).ARM-based Excaliburは,柔軟性のあるプログラマブル・ロジックの領域とハード・マクロのIPコアで構成される領域(プロセッサ・サブシステム)を緊密に統合した製品です(図1).ハードIPのサブシステムは,ARM9コアやキャッシュ・メモリメモリ管理ユニット,周辺回路,メモリ・コントローラなどで構成されています.

本稿では,筆者らがある特定の複雑な設計に対応するためになぜARM-based Excaliburのようなアーキテクチャを選んだのか,また,本アーキテクチャを開発する際に,どのような点が問題となったのかについて解説します.

〔表1〕 ARM-based Excaliburファミリの概要

表にARM-based Excaliburファミリの製品と それぞれの機能を示す.現在,ローエンドの「EPXA1」からハイエンドの「EPXA10」まで,すべてのARM-basedExcaliburデバイスを出荷している.

|

型 名

|

EPXA1

|

EPXA4

|

EPXA10

|

| CPUコア |

ARM922T

|

ARM922T

|

ARM922T

|

| 最大システム・ゲート数 |

263,000

|

1,052,000

|

1,772,000

|

| 標準ゲート数 |

100,000

|

400,000

|

1,000,000

|

| ロジック・エレメント(LE) |

4,160

|

16,640

|

38,400

|

| エンベデッド・システム・ブロック(ESB) |

26

|

104

|

160

|

| プログラマブル・ロジック領域のRAM(ビット) |

53,248

|

212,992

|

327,680

|

| シングルポートSRAM(Kバイト) |

32

|

128

|

256

|

| デュアルポートSRAM(Kバイト) |

16

|

64

|

128

|

| ユーザI/O数 |

186/246

|

434/496

|

711

|

| パッケージ(FineLine BGA) |

484ピン/672ピン

|

672ピン/1,020ピン

|

1,020ピン

|

〔図1〕ARM-based Excaliburデバイスのダイ

ARM-based Excaliburデバイスのダイの写真.ハードIPのプロセッサ・サブシステム(Stripe)の領域とプログラマブル・ロジックの領域に分かれている.