CPUコア搭載FPGAが存在を誇示 ――Embedded Systems Conference San Francisco 2002現地

2002年3月12日~16日に米国カリフォルニア州San FranciscoのMoscone Centerにおいて組み込みシステム関連の展示会「Embedded Systems Conference(ESC) San Francisco 2002」が開催された.米国Xilinx社のVertex-II Proや米国Altera社のARM-based Excaliburなど,CPUコアを搭載したFPGAのデモンストレーションが相次いで行われた.

●Xilinx,PowerPC搭載FPGAとWindRiver製ICEを接続

米国Xilinx社は,2002年3月に発売を開始したPowerPCプロセッサ内蔵FPGA「Virtex-II Proファミリ」のデモンストレーションを行った.エンジニアリング・サンプルを実装した評価ボードとJTAGポート経由でCPUコアにアクセスする米国WindRiver社製ICE(in-circuit emulator)「visionPROVE II」を使って,デバッグのデモンストレーションを行った(写真1).このvision PROVE IIは2002年第2四半期から出荷されるという.

[写真1]visionPROVE IIとVertex-II Pro用評価ボード

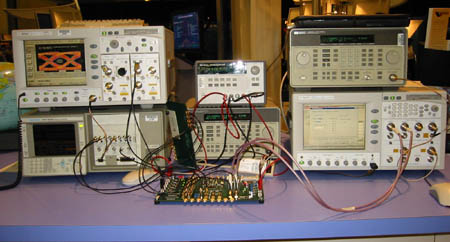

Virtex-II Proファミリは,PowerPCプロセッサだけでなく,622Mbps~3.125Gbpsの伝送速度に対応したシリアル・トランシーバ回路も搭載している.こちらのデモンストレーションも行った(写真2).このデモンストレーションでは,ロジック・セル数が11,088で8個のシリアル・トランシーバ回路を搭載する「XC2VP7」を使用.3.125Gbpsの伝送速度におけるアイ・パターンを測定した.

[写真2]3.125Gbpsの伝送速度におけるアイ・パターンを測定

[写真3]ESC San Francisco 2002のXilinxのブース

●Altera,Excalibur用のCPU/周辺回路コンフィグレーション・ツールを展示

米国Altera社は,同社の「Excalibur」が内蔵するCPUコアやその周辺回路のコンフィグレーションとプログラミングを行うためのツール「SOPC Builder」を展示した(写真4).Excaliburには,ARM922Tハード・マクロを内蔵したPLD「ARM-based Excalibur」とソフト・マクロのCPUコアである「Nios」がある.ESC San Francisco 2002では,Excaliburを用いてパソコンとハード・ディスク装置の間でのデータの書き込み/読み出しのデモンストレーションを行った.

[写真4]デモンストレーション(左)とSOPC Builderの画面(右):

CPUやブリッジ,メモリの選択を写真右の画面で行う.緑の丸がついているIPコアはすでにSOPC Builderに入っている.白い丸のIPコアはオプションであり,Altera社やサード・パーティのWebサイトからダウンロードできる.

SOPC Builderによる開発の手順は,以下のとおりである.まずプロセッサの選択(ARM922T,Nios)を行う.次に周辺回路の選択を行う.そしてメモリ・マップやインターフェース・バスの構成を定義する.すると,SOPC Builderがシステムのソース・ファイルを生成する.このときプロセッサ選択でNiosを選べば,プロセッサ,バス,周辺回路をHDLファイルで生成する.ARM922Tの場合はバスと周辺回路のHDLファイル,およびARM CPUのコンフィグレーション・データを生成する.

組み込める周辺回路には,UART,DMA,SRAM(以上,Altera社製)などのほか,ハイスピードとフルスピードに対応したUSB2.0コントローラ(米国Mentor Graphics社製)や,ARMとPCIのホスト・ブリッジ(米国Eureka Technology社製)などがある.

[写真5]ESC San Francisco 2002のAlteraのブース

●Cypress,動的にコンフィグレーションを変更できるマイコンのデモ

米国Cypress Microsystems社は,動的にコンフィグレーションを変更できるマイクロコントローラ「PSoC(Programmable System on Chip)ファミリ」のデモンストレーションを行った(写真6).PSoCは,8ビットCPU,8K~16Kバイトのフラッシュ・メモリ,プログラム可能な12個のアナログ・モジュールと8個のディジタル・モジュールなどを内蔵している.アナログ・モジュールにはコンパレータやフィルタ,D-A/A-D変換回路などがある.ディジタル・モジュールにはタイマやカウンタ,PWMなどが用意されている.デバイスは2001年6月から発売している.一方,PSoCのコンフィグレーションを設定したり,ソフトウェアを開発するためのツール「PSoC Designer」を出荷したのは今年(2002年)2月から.

[写真6]PSoCのデモンストレーション:

三つのPSoCを使用してx軸,y軸,z軸のモータを制御している.

PSoCは動作中にチップ内の機能構成を変えることができる.1チップ当たり最大256とおりの回路構成をプログラムできる.動作時に回路構成を切り替えるには,あらかじめ8ビット・レジスタにタイミングのデータを格納しておく.機能構成の切り替えには最大50μsを要する.

PSoC Designerは,PWMやD-Aコンバータ,フィルタなどの部品ライブラリを備えており,これらを回路図にはめ込んでプログラミングできる.スリープなど特殊な機能が必要なときは,C言語によってソフトウェアで実装する.PSoC DesignerはCD-ROMまたは同社のホームページ(http://www.cypressmicro.com/)より無償で入手できる.

[写真7]ESC San Francisco 2002のCypress Microsystemsのブース

●Tensilica,TIE命令セットを組み込んだMP3デコーダのデモを公開

米国Tensilica社は,同社の「TIE(Tensilica Instruction Extension)技術」を用いたオーディオ・デコーダLSIの開発環境を公開した.TIEとは,独自の記述言語で追加したい拡張命令を定義し,所望のアプリケーションに特化したマイクロプロセッサを生成する技術である.TIEでは47の命令セットが用意されている.

MP3のデコードでは,データ圧縮方式としてハフマン(Huffman)符号化が用いられる(写真8).この部分をTIEなしで設計すると,90クロック・サイクル必要となるのに対して,TIEを用いると1クロック・サイクルで処理できるという.

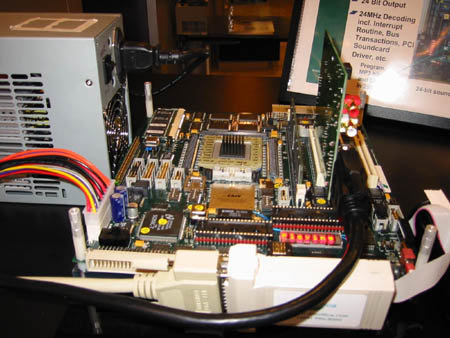

[写真8]TIE技術を用いたMP3デコーダを評価ボードで実現

MP3データ用にカスタマイズされたXtensaをAltera社のFPGAに実装した.24ビット出力.動作周波数は24MHz.

このTIE技術を用いたオーディオ・デコーダLSIの開発環境は,携帯型ヘッドホン・ステレオやセットトップ・ボックス,カー・オーディオなどに応用できる.

[写真9]ESC San Francisco 2002のTensilicaのブース

●Sharp,カラーLCDコントローラを内蔵するARMベースのマイコンを展示

Sharp Microelectronics of the Americas(SMA)は,カラー液晶ディスプレイ(LCD)コントローラを内蔵するマイクロコントローラ「LH79520」と「LH7A400」を発売する.いずれもARMコアを内蔵している.ESC2002のデモンストレーションでは,米国Digi-Frame社のディジタル・フォト・フレームにLH79520が組み込まれていた.ディジタル・フォト・フレームは,ディジタル・カメラやディジタル・ビデオで記録した画像を取り込む写真立てである.Digi-Frame社は,LH7A400の採用も検討しているという.

[写真1>]Digi-Frame社のディジタル・フォト・スタンド:

SMAのLH79520を搭載している.

LH79520は,ARM720Tコア,8Kバイトのキャッシュ・メモリ,MMU,カラーLCDコントローラ,32KバイトのSRAMなどを内蔵している.カラーLCDコントローラは,最大800×600ピクセルのSTN液晶やTFT液晶,高精細TFT液晶に対応している.外部インターフェースとしてUARTとIrDAを備えている.コア電圧は1.8V,I/O電圧は3.3Vである.動作周波数は最大75MHz.2002年3月から量産を開始する予定.

LH7A400は,ARM922Tコアを搭載している.内蔵する周辺回路の構成はLH79520とほとんど同じだが,キャッシュ・メモリが16Kバイト,SRAMが80Kバイトになっている.また,PCMCIAやCompact Flashといったバス・インターフェースに対応する.外部インターフェースとして,UART,IrDA,USB1.1の各機能を備えている.動作周波数は最大200MHz.2002年6月から量産を開始する予定.

[写真11]ESC San Francisco 2002のSharp Microelectronics of the Americasのブース

・Embedde Systems Conference(ESC)のホームページ http://www.esconline.com/