インテグリティな技術コラム(10) ―― トーナメント方式のクロックにおける反射回避方法

前回,メモリのクロック分配方法が,DDR3からは,これまでのトーナメント方式からいもづる方式に変更されたことを述べました.

トーナメント方式はオーソドックスな信号分配方法であり,メモリ以外でも多く用いられています.この方式の波形乱れは,特性の異なる線路の縦続接続により生じているので,計算が可能です.波形乱れが予測可能なら対策も可能ではないかと考えて検討してみたところ,波形乱れを理論的に解決できることが分かりました.以下では,その方法を紹介します.

コラム・連載「インテグリティな技術コラム」 バック・ナンバ

第1回 反射波形にはさまざまな情報が詰まっている

第2回 パルス幅によって変化するノイズの影響

第3回 ラプラス変換による分布定数の解

第4回 ラプラス変換からフーリエ変換へ

第5回 差動インピーダンス

第6回 転換点は10年前,メモリが非同期型から同期型へ

第7回 スタブの反射はSSTLで回避

第8回 メモリ・バスの周波数特性と転送速度

第9回 メモリ・モジュールのクロック分配

●線路の縦続接続には縦続行列を用いる

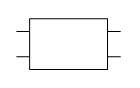

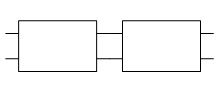

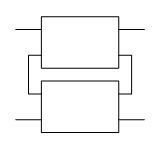

複数の線路を縦続に接続した場合の特性は,縦続行列(F-Matrix)を用いて求めます.F-MatrixのFは,Fundamentalの略です.4端子行列では,インピーダンス行列やアドミタンス行列が比較的ポピュラですが,縦続行列のほうが「基本(Fundamental)」ということのようです.なお,線路を次々に接続することを「直列」と勘違いすることがありますが,図1(a)の4端子回路に対して図1(b)が縦続接続で,図1(c)が直列接続です.混同しないようにしてください.

図1 縦続接続と直列接続

(a) 4端子回路

(b) 縦続接続

(c) 直列接続

縦続接続は,カスケード(cascade)接続ともいいます.4端子回路は,入力端子対と出力端子対の2組の端子で構成されるので,2端子対回路とも呼びます.

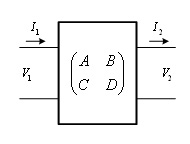

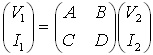

4端子回路の電流の向きは,通常,入力側,出力側ともに回路に流れ込む向きをプラス(+,正)に取りますが,縦続行列だけは,図2に示すように他の4端子行列とは異なり,左から右に向かう向きをプラスに取ります.

図2 縦続行列の電圧と電流

出力側は,回路から流れ出る向きがプラスとなるので,注意してください.

縦続行列は,以下の形で表します.

..... (1)

..... (1)

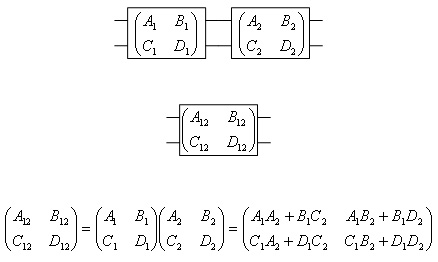

図3のように二つの4端子行列を縦続接続した場合の縦続行列は,二つの行列の積で求めます.

図3 2本線路の縦続接続

さらに三つ以上を縦続接続した場合も同様に,縦続行列を次々に乗算することにより,全体の縦続行列を求めることができます.