インテグリティな技術コラム(2) ―― パルス幅によって変化するノイズの影響

反射波形やクロストークの対策は,多くの場合,ステップ応答または十分に広いパルス幅の応答で考えます.ほとんどの場合はこれでいいのですが,ゲート段数や遅延の差によるハザード(狭い時間幅のパルス)が現れることが想定される場合は,狭いパルス幅に対する応答も考える必要があります.

※ お知らせ

本連載コラムの理解をさらに深められるセミナ「高速ボード設計のためのシグナル・インテグリティ入門――パソコン演習を通して分布定数回路を理解する」が,2010年9月8日(水)に東京・巣鴨のCQ出版セミナ・ルームにて開催されます.

●加える信号のパルス幅が狭いと反射波形の振幅が増大

反射波形には,大きなオーバ・シュートとそれに続く逆極性の跳ね返りが現れます.立ち上がりの場合には,プラス(上に凸 = 山)のオーバシュートとその逆(下に凸 = 谷)の跳ね返りで,立ち下がりの場合には,その反対に,下に凸のオーバ・シュート(谷)とそれに続く上に凸(山)の跳ね返りです.それぞれのパルスの時間幅は配線長の往復の遅延時間で決まります.ボードの配線遅延はおよそ7ns/mなので,7cmの配線ならパルス幅は1ns程度です.通常は,この跳ね返りが大きくならない範囲,すなわちオーバ・シュートでいえば10%~20%になるようにダンピング抵抗の値を選択しています.これよりも大きい,例えば40%のオーバ・シュートでもその跳ね返りは16%で,3.3Vのときに2.8Vまでの落ち込みとなります.これは何とか許容できる範囲でしょう.

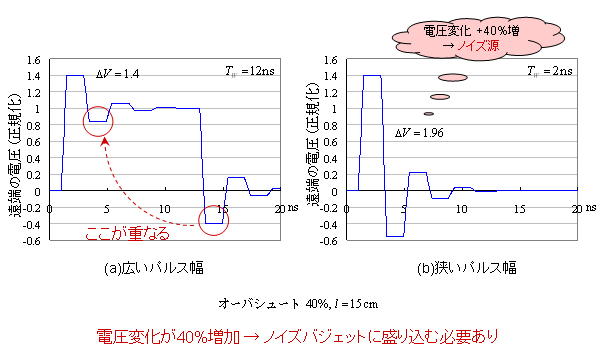

次に,図1(a)に示すような有限のパルス幅の場合を考えてみます.まず,前縁の立ち上がり時に,山と谷とから始まる反射波形が現れます.後縁の立ち下がりでは,谷と山から始まる反射波形が現れます.通常の広いパルス幅の場合,前縁と後縁は時間的に離れているので,独立して考えます.ところが,図1(b)のようにパルス幅が狭くなり,後縁が前縁に近づいてくると,ついには前縁の谷と後縁の谷が重なってしまいます.反射の振動波形のパルス幅と信号のパルス幅が等しくなったときに,このようになります.このとき,40%のオーバ・シュートならば,前縁の跳ね返り(谷)による16%と後縁のオーバ・シュート(谷)が重なり合って,振幅の変化は,196%とほぼ電源電圧の2倍にもなります.

図1 狭いパルス幅と反射の重畳(共振)

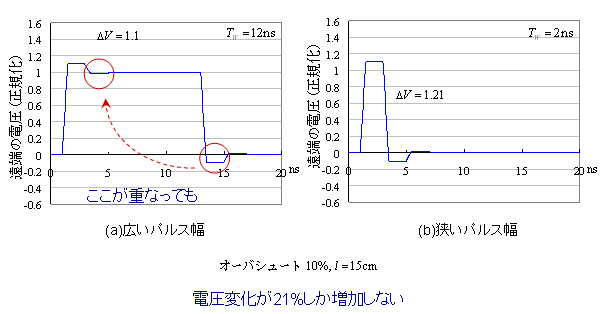

振幅の増大により,グラウンド・ノイズ,同時スイッチング・ノイズ,クロストーク・ノイズなど,全てのノイズが増大します.一般に,電源電圧の2倍もの振幅になるケースは想定外なので,誤動作を引き起こす可能性があります.このような狭いパルスが加えられる可能性のある場合,オーバ・シュートを通常よりも小さく抑えておく必要があります.10%のオーバ・シュートに抑えると,上記のようにパルス幅が重なったときでも,図2に示すように振幅の変化は+21%にしかなりません.

図2 オーバ・シュートを小さく抑えると共振しても大丈夫

●パルス幅が狭いとクロストーク・ノイズも増大する

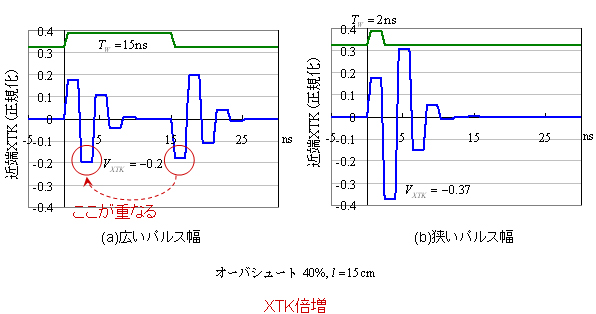

図3(a)は,広いパルス幅に対する近端クロストーク・ノイズです.加害者の立ち上がり信号に対する近端クロストークは,一般に,最初の山,次の谷,さらに3番目の山で収束します.ドライバの駆動能力が大きいと最初の山より2番目の谷のほうが大きな振幅となり,さらに駆動能力が大きいと3番目の振幅が最大になることもあります.図3はやや駆動能力の大きな例で,図1のオーバ・シュート40%に相当します.この場合,2番目の谷の振幅が最大です.加害者の信号の後縁の立ち下がりで,前縁と逆極性のクロストーク・ノイズが生じます.パルス幅が広いときは前縁と後縁が独立していますが,図3(b)の狭いパルス幅では,前縁の2番目の谷と後縁の1番目の谷が重なって,クロストーク・ノイズがほぼ倍増します.

図3 狭いパルス幅の信号によりクロストーク・ノイズが倍増

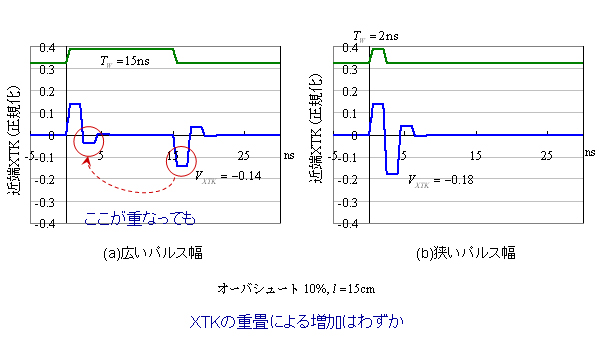

図4は,図2と同様に,オーバシュートを10%に抑えると,前縁のクロストークの2番目の谷が小さくなり,後縁の1番目の谷と重なっても,クロストークノイズの増加はわずかです.

図4 クロストークの2番目の谷を小さくすると重畳しても大丈夫

●遅延素子とANDを入れてノイズを除去

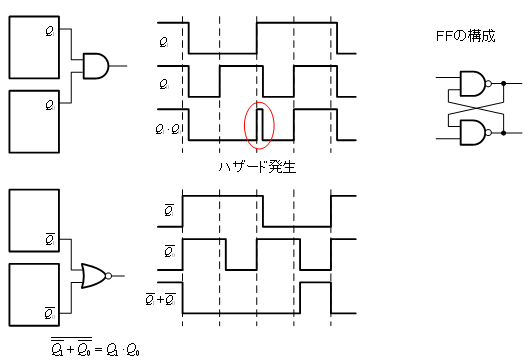

それでは最後に,このようなハザード(ノイズ)が発生しないような回路やハザードを除去する回路を紹介しておきましょう.図5は4進カウンタの例です.8進でも10進でも16進でも同様です.カウンタを構成するFF(フリップフロップ)の出力を,それぞれQ1,Q0とすると,Q1Q0="11"となる論理は,

![]()

です.FFは,通常,NANDゲートのたすき掛けで構成されるので,基本的に立ち下がりが立ち上がりよりも内部ゲート1段分遅くなります.従って,上式の論理をそのまま取ると,Q1の立ち上がりとQ0の立ち下がりのタイミングでQ1Q0="11”の状態が生じて,ハザードが発生します.これを回避するには,ド・モルガン(De Morgan)の法則を用いて,

![]()

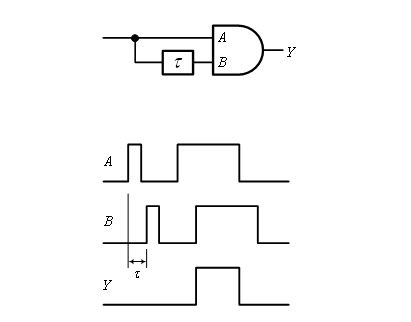

とすればよいわけです.発生してしまったハザートを除去する回路を図6に示します.信号をτだけ遅延させて元の信号とANDをとります.遅延時間τにより除去できるハザードの最大パルス幅が決まるので,状況に応じてτを選択すればよいわけです.これは正のハザードを除去する方法ですが,負のハザードを除去する方法は読者の皆さんが各自で考えてください.

図5 カウンタの論理の取り方

図6 正のハザードの除去回路

うすい・ゆうぞう

シグナル インテグリティ コンサルタント

http://home.wondernet.ne.jp/~usuiy/

◆筆者プロフィール◆

碓井 有三(うすい・ゆうぞう).1972年,富士通株式会社入社.回路技術部長,テクノロジ本部主席部長などを経て,2001年に退社.同年,株式会社マクニカ入社.同社CTOなどを経て,2008年退社.現在,フリーのコンサルタント.