インテグリティな技術コラム(6) ―― 転換点は10年前,メモリが非同期型から同期型へ

歴史を振り返ると,高速回路の技術にいくつかの転換点があったことが分かります.ここでは1999年ころに生じたメモリの変化について説明します.

コラム・連載「インテグリティな技術コラム」 バック・ナンバ

第1回 反射波形にはさまざまな情報が詰まっている

第2回 パルス幅によって変化するノイズの影響

第3回 ラプラス変換による分布定数の解

第4回 ラプラス変換からフーリエ変換へ

第5回 差動インピーダンス

現在のメモリは,ほとんど全てが同期型ですが,10年ちょっと前のメモリは,クロックを持たない非同期型でした.以前から,メモリ以外のロジック(論理回路)は,一部を除いてクロック同期でした.クロック同期の利点は,セットアップ時間とホールド時間の間に論理が確定していれば,それ以外のタイミングで波形の乱れを許容できる点です.これにより,配線設計が比較的楽になります.ただし,部分的に速い回路があっても,最も遅い論理に合わせてクロック周期を設定しなければならないので,極限の性能を求めることはできません.

一方,非同期回路はクロックを待たなくてよいので,論理が確定すると,次のステップに進むことができます.性能は極限まで引き出せますが,波形の乱れに弱く,途中で波形割れが生じると,論理が変化したのか,ノイズなのか,区別がつきません.そのため,配線設計に非常に注意を払う必要があります.

従って,昔の非同期型メモリの回路設計では,一般的な論理回路設計とは別の,特殊な知識が必要でした.

●現在のメモリの主流はDDR SDRAM

現在のパソコンのメモリは,そのほとんどがDDRメモリです.DDRとはご存じのとおり,「Double Data Rate」の頭文字です.クロックの立ち上がりと立ち下がりのそれぞれのタイミングでデータをやりとりします.実際には,メモリ内部のDLL(Delay-locked Loop)によって,クロック波形の立ち上がりと立ち下がりの両方に相当するタイミングを生成し直しています.

これをメモリに適用したものが,DDR SDRAMです.SDRAMは「Synchronous Dynamic Random Access Memory」です.DDR2やDDR3は,電圧やクロック周波数の異なる派生版として規格化されています.

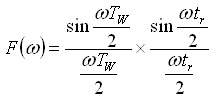

ところで,なぜDouble Data Rateなのかを考えてみます.パルス波形を伝送するには,そのパルス波形に対応する周波数帯域を必要とします.時間領域のふるまいを周波数領域の現象として考えるには,フーリエ変換を用います.パルス幅TW,立ち上がり時間trのパルス波形の周波数スペクトルF(ω)は,

.....(1)

.....(1)

となって,パルス幅TWと立ち上がり時間trだけに依存します.データが100MbpsのSingle Data Rateの場合のデータとクロックの周波数スペクトルを図1に示します.データとクロックの配線のトポロジ(配線形態)が異なるので同列には論じられませんが,クロックとデータには2倍の違いがあるので,データをもっと詰め込んで,2倍にして送ろう,そんな発想です.この考え方はかなり昔から,「多相クロック」という概念で存在していました.すなわち,クロックの位相をずらして,最適のタイミングでデータを取り込むような仕組みです.

図1 データとクロックの周波数スペクトラム

●それ以前は非同期メモリ

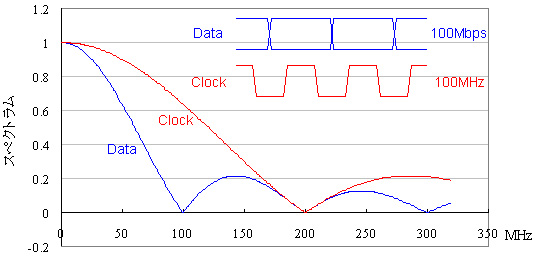

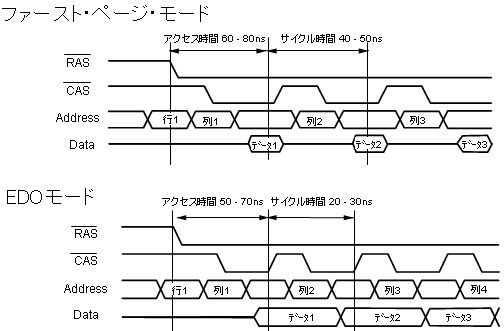

メモリは,プリフェッチやレイテンシなど,ほかの論理回路にはない概念があるものの,クロック同期なので,一般の論理と同じように設計できます.ところが,SDRAM登場以前のメモリにはクロックの概念がなかったので,メモリ回路の設計は一般の論理回路とは別の設計者が担当していたケースが多かったようです.図2はこの古典的なDRAMの構成で,図3はタイミング図です.ファースト・ページ・モードで従来より読み出しが速くなり,その後,EDO(Extended Data Out)モードにより出力回路を工夫して,連続読み出し速度を向上させました.

図2 古典的な(SDRAMより前の)DRAMの構成

図3 古典的なDRAMのタイミング

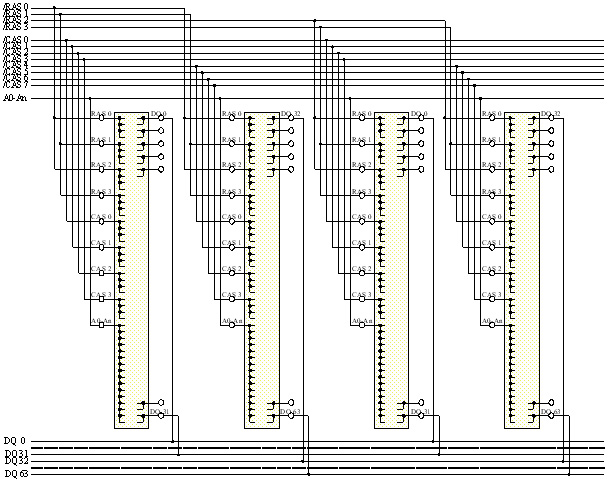

メモリICは,現在と同じようにメモリ・モジュール上に搭載され,そのモジュールがパソコンのメイン・ボードに実装されていました.ただし当時は,このモジュールのコネクタは,電極が1列(表裏同じ電極)だったのでSIMM(Single In-line Memory Module)と呼ばれていました.図4はそのSIMMを4枚使用した例です.データ線のサフィッスクを見ると分かるように,上位32ビットと下位32ビットが1組として使用されています.