マルチプロセッサで実現したH.264ビデオ・デコーダ ――コンフィギャラブル・プロセッサのユーザ定義命令とオンチップ・バスを活用

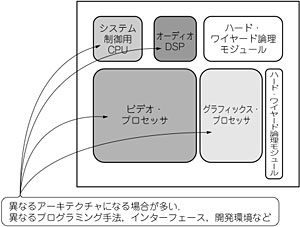

機能分割とは,図1に示すように,設計するシステム仕様を機能的に切り分け,各プロセッサに割り振る方法です.携帯電話向けなどのシステムLSIの多くは,機能分割タイプに相当します.例えば,システムを制御するプロセッサとデータを処理するDSPを,一つのLSIにまとめたような構成です.

図1 機能分割型マルチプロセッサLSI

システム制御,オーディオ処理,ビデオ処理,グラフィックス表示と機能的に切り分け,各プロセッサに割り振る.機能ごとにアーキテクチャが異なるプロセッサが使われる場合が多い.

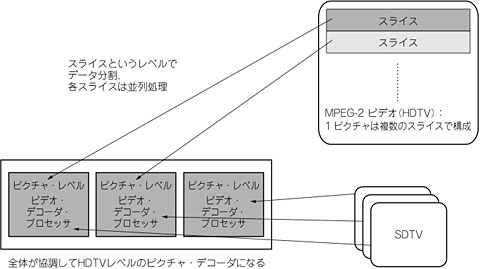

データ分割とは,データのあるかたまりを複数のプロセッサで同時に処理することで,処理能力を高めるというような方法です.図2には,高精細テレビ(HDTV:high definition television)のMPEG-2ビデオ・デコーダの例を示しています.ここでは,スライスというデータ・セットを三つのプロセッサに割り振っています.もちろん,HDTVのMPEG-2ビデオ・デコーダを処理フローに従って機能分割することも可能です.実際には,図3に示すように,システム仕様によって適切な構成を見つける必要があります.

図2 データ分割型マルチプロセッサLSI

高精細テレビ(HDTV)デコーダの例を示す.1本のHDTVビット・ストリーム,もしくは3本の標準テレビ(SDTV)ビット・ストリームを同時にデコード可能な構成である.3個のプロセッサをそれぞれ独立したMPEGデコーダとして設計した.HDTVビット・ストリームでは,一つのプロセッサをマスタとし,スライス・レベルのデータを各プロセッサのMPEGデコーダで処理させる.SDTVビット・ストリームは一つのプロセッサで処理できるので,本LSIでは三つのビット・ストリームを同時にデコードできる.

図3 マルチプロセッサLSI設計の検討点

HDTVデコーダを例に,検討点を示している.ピクチャ,GOP,シーケンスの各レベルは,デコード処理上クリティカルではないので除外している.