無償ツールで設計効率の向上を体験 ―― 配線レイアウトの電磁界シミュレーションを体験する

tag: 実装 電子回路 ディジタル・デザイン

技術解説 2009年6月25日

3. 配線の曲がり部(コーナ)のシミュレーション

● 配線を曲げてみる

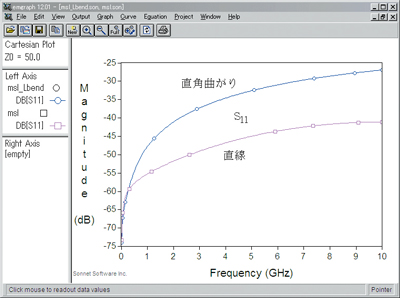

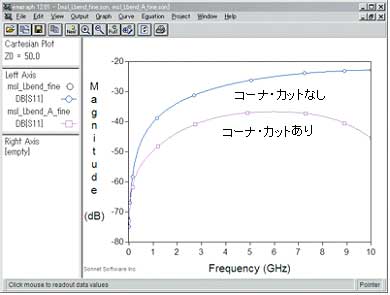

図23は,MSLを直角に曲げたモデルです.配線を2本描いてつないだものです.結果のS11を表示してから,「File」→「Add File(s)...」で先の直線のMSLの結果を追加すると,図24のようにグラフ上で比較できます.明らかに直角曲がりのMSLは反射が大きくなりました.これはコーナで電磁界の分布が乱れてインピーダンスが急に変化することで反射波が増えるからだと考えられます.

図23 MSLを直角に曲げたモデル

図24 直線と直角曲がりのMSLのS11を比較する

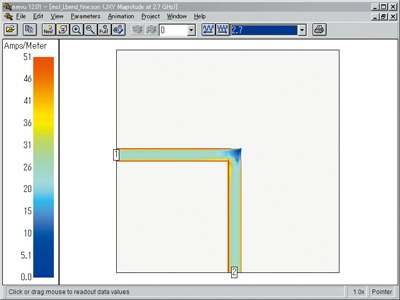

図25はMSL表面の電流分布です(コーナを詳細に調べるため,セルをより細かい0.02mmに設定した.16Mバイト以内に収まるので試してみよう).配線の両縁には強い電流が流れ,コーナでは内側寄りに偏っています.このように配線のコーナは,電磁波が内側を通ることで位相遅延時間が短縮されるという現象が起きます(5).

図25 MSL表面の電流分布

● コーナ・カットによる影響

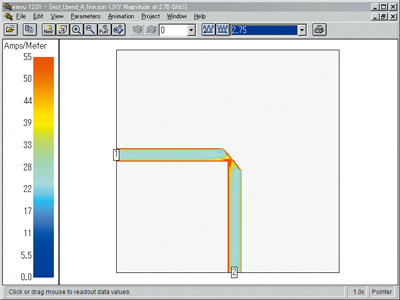

図26はコーナの外側をカットしたMSLの表面電流分布です.コーナの両縁に強い電流が認められます.図27はコーナ・カットがないMSLのS11との比較です.カットによって反射波が減少していることが分かります.

図26 コーナの外側をカットしたMSLの表面電流分布

図27 コーナの外側をカットしたMSLとコーナ・カットがないMSLにおいてS11を比較

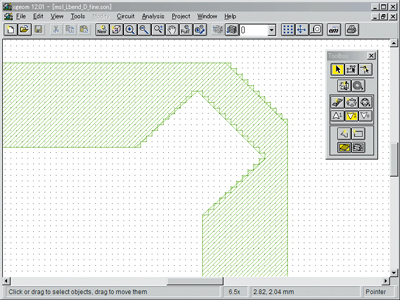

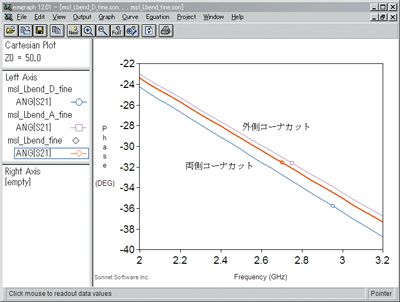

図28はコーナの内側と外側の両コーナをカットしたモデルです(5).また図29はS21の位相角の比較です.両側コーナ・カットは外側コーナ・カット(図26)よりも位相角が大きくなりました.

図28 コーナの内側と外側の両コーナをカットしたモデル

図29 S21の位相角の比較

この位相角を使えば,位相遅延時間Tpdは,次の式で求められます.

![]() ・・・・・・・・・・・・・・・・・・・・ (1)

・・・・・・・・・・・・・・・・・・・・ (1)

ここではfは周波数[Hz],Angは位相角[°].

式(1)は,例えば2.5GHzではsin波の1サイクル(=360°)に要する時間が1/(2.5×109)=0.4[ns]なので,360°に対する位相角の割合で位相遅延時間を得るという意味です.

図29のグラフ上にマウス・カーソルを置いて直読すると,2.5GHzで外側コーナ・カットは-28.7°,両側コーナカットは-30.3°です(マイナスは遅延を表す).式(1)から11.5nsと12.1nsが得られますが,これらが無視できるかは信号の速度によります.

高速ディジタル回路で複数の信号間のタイミングを合わせるためにミアンダ・ライン注8を使うとコーナの数が増えるので,動作周波数によっては位相遅延時間の検討が必要になるでしょう.

注8: ミアンダ・ラインはジグザグに蛇行した配線で,線路を長くすることにより信号の遅延を調整できる.