ディジタルFMステレオ・チューナの製作 ―― 雑誌の付属基板でここまでできる

tag: 半導体 ディジタル・デザイン

技術解説 2009年6月 5日

● ステレオ復調回路

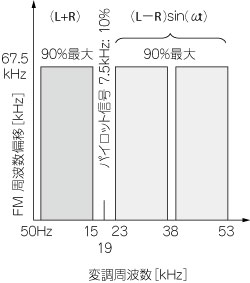

FMステレオ放送はモノラルの放送との互換性を保つため,通常の音声信号の周波数帯域(50Hz~15kHz)には左チャネルと右チャネルの信号を加算したL+R信号を変調します.左チャネルと右チャネルの差の信号であるL-R信号は38kHzを中心とする30kHz幅(23kHz~53kHz)の周波数帯域に38kHzの副搬送波を抑圧したDSB信号として加えています.受信機側で,この抑圧された38kHzの副搬送波を正確に復元するために,その半分の周波数である19kHzの信号を「パイロット信号」として,一定レベルで送出することも行っています.このようなL+R信号,L-R信号,パイロット信号を合成,加算した信号をコンポジット信号と呼ぶこともあります.図24にコンポジット信号の周波数スペクトルを示します.

[図24] FMステレオ・コンポジット信号のスペクトル

L+R信号,L-R信号,パイロット信号の三つの成分から成る.76kHzにはDARCというVICS交通情報などのデータ放送も実施されていることがあるが,この図では省略.

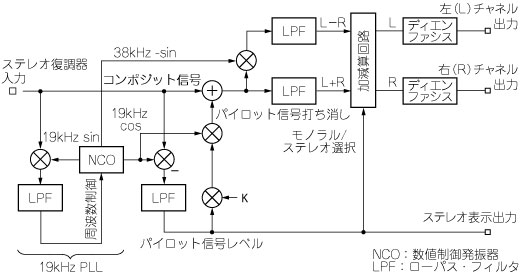

今回のディジタル信号処理によるFMステレオ復調器では,原理に忠実に,38kHz の副搬送波をPLLによって再生したのち,この副搬送波によってL-R信号を復元します.その後L+R信号とL-R信号を加減算することで左(L)チャネル信号,右(R)チャネル信号を取り出すようにしています.

図25にステレオ復調器のブロック図を示します.ステレオ復調器には送信側の38kHzの副搬送波を復元するための発振器としてNCOを用意し,19kHzのsin信号とcos信号,38kHzのsin信号の出力が取り出せるようにします.このNCOは初段の複素ミキサで行ったように正弦波のテーブルを使用して正弦波を生成するのではなく,FM復調で使用したCORDICを利用して,位相情報(角度)からsin信号とcos信号を生成するようにしています.38kHzのsin信号は三角関数の倍角の公式を用い,sin信号とcos信号の積から生成します.

[図25] ステレオ復調器のブロック図

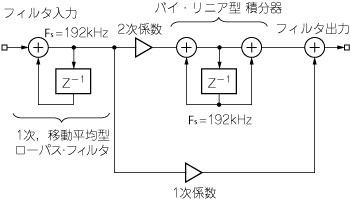

NCOの19kHz sin信号とコンポジット信号を乗算し,コンポジット信号に含まれる19kHzのパイロット信号との位相比較を行います.乗算器の出力には,NCOの19kHz sin信号と19kHzパイロット信号の位相差に対応する情報が含まれています.そのためループ・フィルタによって制御に必要ではない成分は除去し,積分を行って,NCOの周波数制御信号を生成しPLLを構成します.図26はループ・フィルタのブロック図です.このループ・フィルタ部だけで独立したHDLブロックとしました(loop_fil.vhd).

[図26] ステレオ復調の19kHz PLLループ・フィルタの構成

パイ・リニア型と呼ばれる積分器を使用し,残留位相誤差が0に近づくように構成した.

19kHzのcos信号は同様にコンポジット信号と乗算し,ローパス・フィルタを通すことで,パイロット信号の振幅に対応する信号が得られます.そこでこの振幅情報をもとに,コンポジット信号中のパイロット信号を打ち消し,消去するための19kHzの正弦波を生成します.こうすることにより,急しゅんなフィルタを用意することなく,不要な19kHzパイロット信号を取り除けます.

このパイロット信号の振幅情報はステレオ放送であることを示すインジケータ用の信号にもなります.パイロット信号が存在しない時は,この後に続く加減算回路の動作を停止し,L-Rの信号を使わないようにします(L,RどちらのチャネルにもL+R信号を出力する).

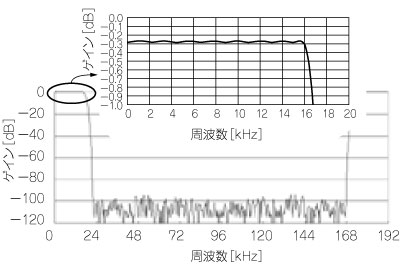

パイロット信号を取り除いたコンポジット信号と,先の38kHz sin信号(副搬送波)を乗算することでL-R信号が復元できます.図27は最終的にL+R信号,L-R信号を取り出すために用いた,カットオフ周波数16kHzのローパス・フィルタの特性です.やはり192タップのFIRフィルタで構成されています(dfir192.vhd).L+R信号,L-R信号が復元できれば,これらの信号の和,差を計算することによってLチャネル信号,Rチャネル信号が生成できます.

[図27] L+R信号,L-の信号を通す,最終フィルタの特性

192タップのFIRフィルタ.

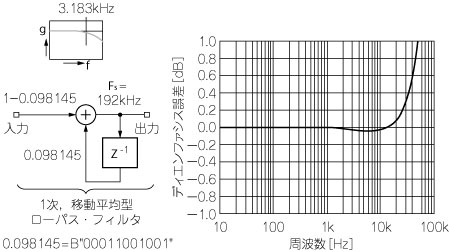

FM放送では,変調する信号の高い周波数成分をあらかじめ強調して送信(エンファシス)します.受信側ではそれと反対の周波数特性を持った回路で高い周波数成分を減衰(ディエンファシス)させることでノイズの低減を行います.今回のディエンファシス回路は,1次の移動平均型のフィルタで実現し,周波数特性を近似しています.図28はその回路と,本来の特性(50μsの時定数を持った1次のローパス・フィルタ)との誤差を示したものです.ここでは 0.98145 という固定の定数に対する乗算が必要になりますので,固定のシフト演算を使ったHDL記述で実現しています(dmodmpx.vhdの後半).

[図28] ディエンファシス回路の構成と特性

1次の移動平均型フィルタとして構成.

● S/PDIFデータ生成,I2Sデータ生成

ステレオ分離回路によって左チャネルと右チャネルに分離されたオーディオ信号は,Fs=192kHzの20ビット幅の並列データとなります.

S/PDIFディジタル・オーディオ・インターフェースに対しては,Fs=48kHzの信号としてシリアル・データに変換して送出します(spdif20_cnv.vhd).D-Aコンバータの入力フォーマットであるI2Sフォーマットに対しては,Fs=96kHzの信号としてシリアル・データに変換して送出します(i2s20_cnv.vhd).