ディジタルFMステレオ・チューナの製作 ―― 雑誌の付属基板でここまでできる

tag: 半導体 ディジタル・デザイン

技術解説 2009年6月 5日

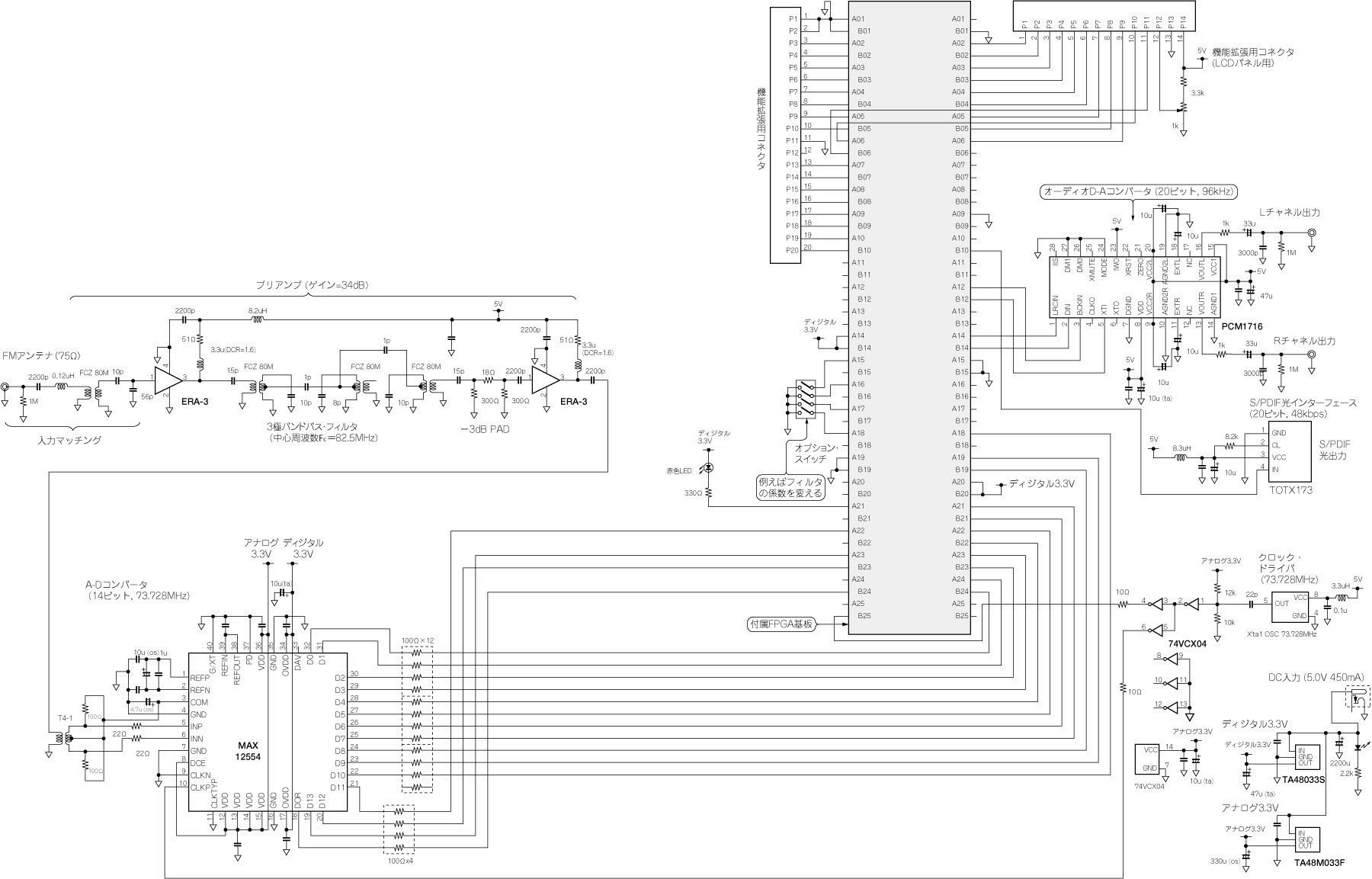

● 回路について

図1は今回製作したFMステレオ・チューナの全体の回路図です.

[図1] FMステレオ・チューナの回路図 *クリックすると拡大します.

アンテナからの入力信号は,米国Mini-Circuits社の「ERA-3」というMMICを用いて2段増幅し,約34dBの増幅度を得ています.2段の増幅段の間には三つの同調回路からなるバンドパス・フィルタを挿入しています.

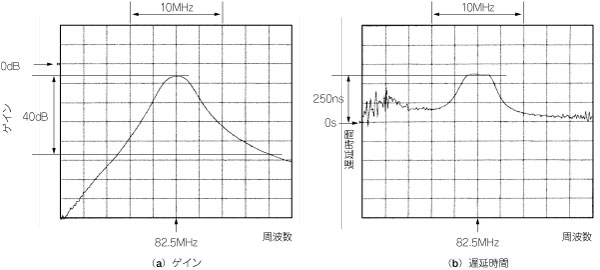

図2は市販の可変コイルを用いて作ったバンドパス・フィルタの周波数特性の測定結果です.回路図に示した回路定数であれば,可変コイルのコアの調整だけで日本国内のFM放送帯の周波数(76MHz~90MHz)のうち,2MHz程度の帯域を平坦な遅延特性で同調が可能です.

[図2] 高周波増幅部のバンドパス・フィルタの周波数特性

ネットワーク・アナライザによる測定結果

高周波増幅部の出力信号は,パイプライン方式の高速A-Dコンバータによってディジタル信号に変換します.今回は,FM放送帯の周波数を低い周波数に変換してからA-D変換するのではなく,受信信号を直接サンプリングします.A-Dコンバータのサンプリング周波数として73.728MHzを用いた場合,受信周波数である76MHz~90MHzの信号は2.272MHz~16.272MHzの信号としてA-Dコンバータのディジタル出力に現れることになります(第3ナイキスト・バンドをアンダ・サンプリング).

今回A-Dコンバータとしては,米国Maxim Integrated Products社の「MAX12554」を用いていますが,米国Analog Devices社の「AD9245」や米国Texas Instruments社の「ADS6143」などでも同様に使用できます(ただしピン配置や使用方法は異なる.回路,パターン変更の必要あり).

ディジタル信号になった受信信号は付属FPGA基板に送られ,ディジタル信号処理によって最終的に左右のチャネルに分離した20ビット長のオーディオ信号を生成し,付属FPGA基板から出力します.このFMステレオ・チューナの主となる出力は光ディジタル・インターフェースS/PDIFによるディジタル出力(Fs=48kHz)です.外部にオーディオ用D-Aコンバータを接続して使用することを想定していますが,受信機基板上にもD-Aコンバータを実装し,受信基板から直接アナログ出力を得ることもできます.D-Aコンバータは,Texas Instruments社の「PCM1716」で,サンプリング周波数96kHzで動作させています.

付属FPGA基板上には3.3Vの電源電圧で動作する水晶発振器を搭載するスペースが用意されていますが,今回は水晶発振器を受信機基板側に搭載しています.これは,73.728MHzという一般的ではない周波数の水晶発振器を特注する際,3.3V動作の発振器は短期間に製作してもらうことができず,やむなく5V動作の発振器を使用しているためです.受信機基板上では5Vの発振出力振幅を3.3Vへ変換するため,発振器からの出力は容量結合による分圧器を通してインバータ(74VCX04)を駆動し,その出力をA-DコンバータとFPGA基板に供給しています.

受信機基板上には3.3Vの定電圧電源回路を2系統用意しています.FPGA基板を含むディジタル系とA-Dコンバータ用のアナログ系で電源を分離するためです.高周波増幅部とオーディオD-Aコンバータは5Vの電源で直接動作させています.今回の試作機の消費電流はトータルで約450mAになりました.