ディジタルFMステレオ・チューナの製作 ―― 雑誌の付属基板でここまでできる

tag: 半導体 ディジタル・デザイン

技術解説 2009年6月 5日

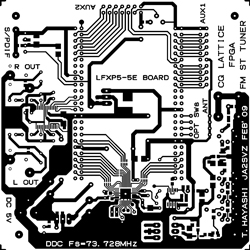

● プリント基板の作成と部品の実装

今回の受信機基板は,筆者が使い慣れたフリー・ソフトウェアのプリント基板設計用ツールである「PCBE」を用いてパターンを設計しました.図3にプリント・パターンを示します.PCBEの基板設計データは付属DVD-ROMに収録してありますので,ファイトのある方はぜひプリント基板の製作にも挑戦してみてください.

[図3] プリント基板パターン

フリー・ソフトウェアのプリント基板設計用ツールPCBEを用いてパターンを設計した.1層,銅箔面.

今回の試作基板は片面パターンの基板として設計してあります.最小パターン間距離は0.5mmです.筆者はサンハヤトの感光基板を用いて,露光,現像,エッチングの工程を経て自作しました.

プリント基板の製作まではとてもできない,という方のため,このFMステレオ・チューナの基板を両面基板としてプリント基板製造会社に製造をお願いし,水晶発振ユニットと1組にして頒布することを計画しています.準備ができましたらディジタル・デザイン・テクノロジ本誌のWebサイトでお知らせします.

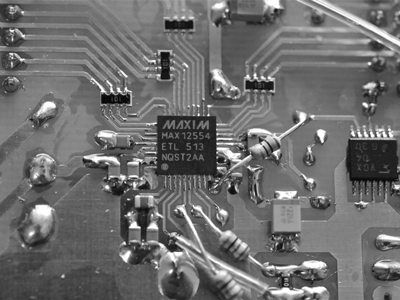

なお,今回使用したような高速A-Dコンバータは多くの場合,QFNと呼ばれるリード線のない,超小型のパッケージで供給されています.QFNのICをプリント基板に手作業ではんだ付けするには一定の技術レベルが要求されます(写真3).

[写真3] A-Dコンバータ

リードのないQFN,ピンのリッチは0.5mm.

● FPGAに実装する回路の開発

FPGAの設計環境としては,米国Lattice Semiconductor社のFPGA設計ツール「isp LEVER 7.1 Starter」を使用しました.ispLEVERを使用するのは初めてでしたが,使いやすい環境で,特に大きくつまずくこともなく設計を完了できました.

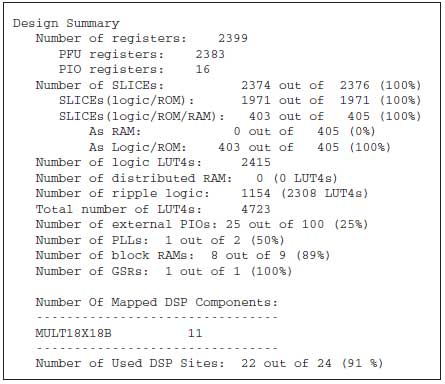

図4に配置配線後のFPGAリソースの使用の様子をまとめます.スライス(SLICE)はほぼ100%を使い切っていて,このXP2-5Eに搭載する設計としては,最大規模の設計になりました.

[図4] FPGAのリソースの使用状況

SLICEはあと二つしか残っていない.さらに回路を追加する場合は,フィルタのアキュムレータのビット幅を削減するか,出力回路をS/PDIFかI2Sのどちらか一方にする方法がある.

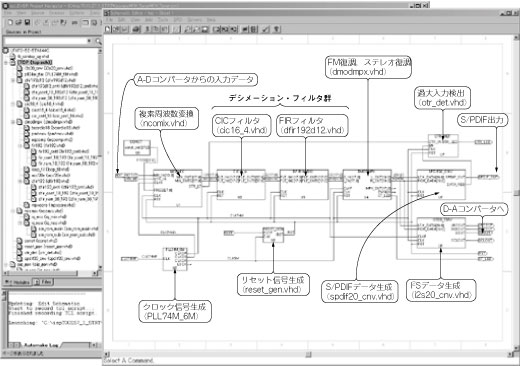

図5はispLEVERの回路図エディタで描いた,FPGAに搭載する回路のトップレベルの回路図です.画面に表示されているトップレベルより下の階層はすべてハードウェア記述言語のVHDLで記述しています.このispLEVERの設計データについても,付属DVD-ROMに収録してあります.お持ちのパソコンにispLEVERをインストールし,HDLコードを確認しながら記述の内容を確認してください.

[図5] ispLEVER Starterで記述したFPGAのトップレベル回路図