ディジタルFMステレオ・チューナの製作 ―― 雑誌の付属基板でここまでできる

tag: 半導体 ディジタル・デザイン

技術解説 2009年6月 5日

4.ディジタル信号処理部の詳細

FPGA内部のディジタル信号処理部はVHDLを用いて記述しました.FPGAに用意されたDSPブロック(今回は18ビット×18ビットの乗算器のブロックとして利用することが主になった)や組み込みブロック・メモリ(EBR)を有効に使うようにしました.VHDLのソース・コードは付属DVD-ROMに収録されていますので,図5のトップレベルのブロック図を参考にしながら記述を追ってみてください.

● NCOと複素ミキサによる複素周波数変換(ncomix.vhd)

A-Dコンバータでディジタル信号に変換した受信信号(RF)は,直交2相の局部発振信号(LO)と乗算することで 0Hzを中心としたベースバンド信号に周波数変換します.局部発振器にはNCOと呼ばれるディジタル的な発振器を用います(iq_nco.vhd).NCOはクロックごとにその値を更新する位相アキュムレータと,正弦波の波形を生成する正弦波波形ROMから成ります.実用的な14ビット~18ビットの分解能を持った正弦波波形のデータは,膨大な量のデータとなりますので,ROMの大きさを現実的な大きさに抑えるためには,なんらかの工夫が必要です.

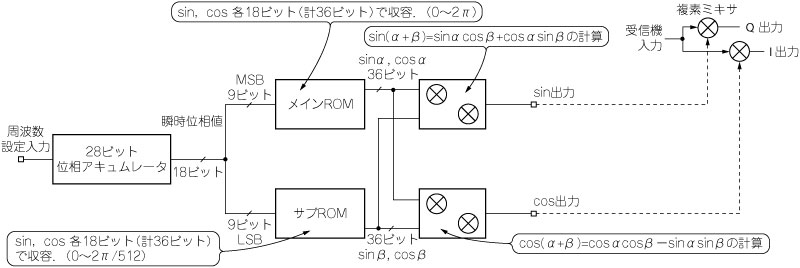

受信機の最初のステージに使用するNCOは,受信機の中でも最も動作速度が要求されますので,ROMサイズの縮小の方法にはあまり選択の余地はありません.筆者は三角関数の加法定理を用いて,正弦波波形ROMの大きさを縮小する方法をよく使います.二つの36ビット幅,512ワードのROM(360°全周のデータを格納するメインROMと全周の1/512の詳細データを格納するサブROM)を用いることで,18ビット精度のsin波,cos波を同時に生成します.図12にこの工夫を採り入れたNCOのブロック図を示します(iq_nco.vhd).複素ミキサはDSPブロックの要素として用意されている18ビット×18ビットの乗算器を2個,I信号,Q信号生成用に用いています(iq_mix.vhd).

[図12] 三角関数の加法定理を用いるNCOのブロック図 *クリックすると拡大します.

4個の乗算器を使用している.複素ミキサで使用する2個を合わせると6個となり,フロントエンド部分でFPGAの乗算器リソースの50%を使ってしまう.

なお,NCOの出力周波数は受信周波数と合わせる必要があります.現在は82.5MHzを受信するよう,28ビットの周波数設定データはX"1E75555"(16進)に設定されています(const.vhd).