ディジタルFMステレオ・チューナの製作 ―― 雑誌の付属基板でここまでできる

tag: 半導体 ディジタル・デザイン

技術解説 2009年6月 5日

3. シミュレーションによる設計の検証

今回のFMステレオ・チューナの開発では,各部のHDL記述の段階から徹底してシミュレーションを実施し,最終的にはFMチューナ全体のHDL記述に対しA-Dコンバータ出力に相当するFM変調信号を与えることで,FM受信機としての性能を評価しました.

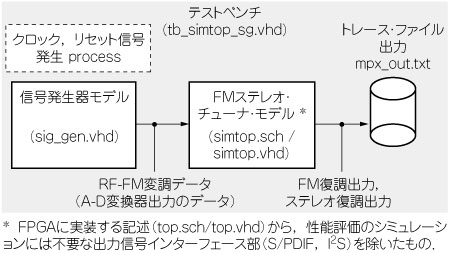

FM変調信号の発生回路はVHDLで記述し,それをテストベンチにインスタンシエーションして,受信機本体の回路と同時に実行,シミュレーションするようにしています.このFM変調信号発生回路はFPGA上に合成が可能で,このFPGAとD-Aコンバータを接続することで,アナログ信号としてのFM変調信号を生成することもでき,A-Dコンバータも含めた,受信機全体のアンテナ端子からの性能も評価可能になります.これらの検証の方法を図10にまとめます.

[図10] HDLシミュレーションのテストベンチの構造

信号発生器モデルはFPGAに合成可能であり,その出力にD-Aコンバータを接続して実際の(アナログ)信号発生器としても使用する.

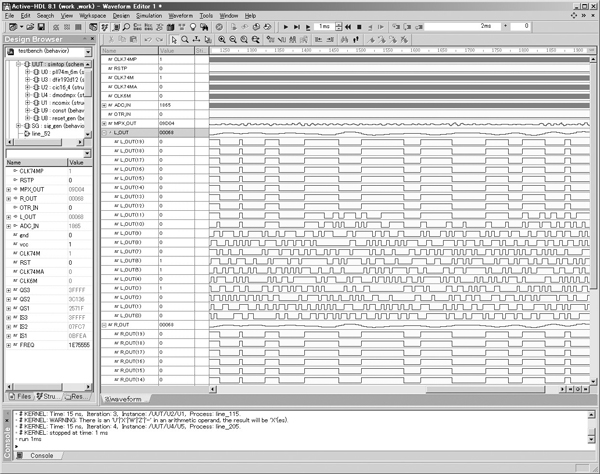

ispLEVERには米国Aldec社のHDLシミュレータ「Active-HDL」のOEM版が付属しています.図11はActive-HDLを使ってトップレベルのテストベンチ(tb_simtop_sg.vhd)を読み込み,シミュレーションを開始した様子です.

[図11] ispLEVERで利用できるAldec社のHDLシミュレータ Active-HDL

ispLEVERにはOEM版が付属.回路規模が大きくなるとシミュレーション速度に制約がかかる.

このFMステレオ・チューナはXP2-5Eの容量をほぼ使い切る設計規模になりました.このためActive-HDL LWEの設計規模の制約を超えてしまい,シミュレーション速度がかなり低下(本来の速度の1%)します.このため筆者は,回路全体のシミュレーションにはActive-HDLの製品版を使って行いました.製品版のActive-HDLであれば,実時間600msのシミュレーションが約2時間で完了できます.600ms程度のシミュレーションでステレオ信号の復調,ひずみ率,ステレオ分離度,S/Nの測定は十分行うことができます.