ディジタルFMステレオ・チューナの製作 ―― 雑誌の付属基板でここまでできる

tag: 半導体 ディジタル・デザイン

技術解説 2009年6月 5日

● CICフィルタとFIRフィルタによるデシメーション・フィルタ

今回のFMステレオ・チューナではサンプリング周波数Fs=384kHzでFM復調を行います.A-Dコンバータのサンプリング周波数である73.728MHzから,384kHzまでサンプリング周波数を落とす,つまり192分の1のデシメーションを行うことになります.このような高い比率のデシメーションを行うためには,非常に高い次数のフィルタを用いて急しゅんなローパス・フィルタ特性を実現する必要があります.こういった場合によく行われる方法は,CIC(Cascaded Integration-Comb)フィルタを用いて,ある程度デシメーション(今回は1/16)した後,通過帯域が平坦な特性を持っているFIR(Finite Impulse-Response)フィルタを使用してさらにデシメーション(1/12)する方法です.

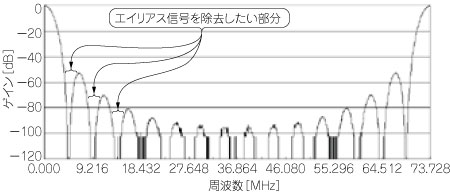

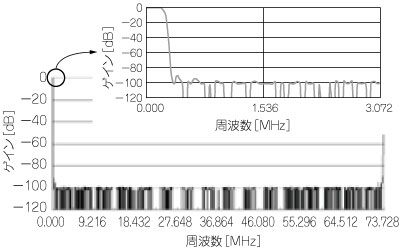

図13に今回実装したCICフィルタの周波数特性(実測)を示します.CICフィルタは積分器と微分器を接続したSINCフィルタのユニットを複数,カスケードに接続したもの(図14)ですが,微分器の遅延の段数によって,減衰得特性の極(ノッチ)の位置を調整できます.この例では微分器の遅延段数を16としているため,73.728M/16=4.608MHzごとにノッチが現れます.このことは以降のステージでFs=4.608MHzで処理を継続する場合,0Hz付近に折り返してくるエイリアス成分が効果的に取り除かれていることを意味します(cice16_4.vhd).

[図13] CICフィルタの特性令

微分器の遅延段階数を16としてあるので,Fs/16=4.608MHごとに減衰特性にノッチを生じる.カスケード段数は4とした.

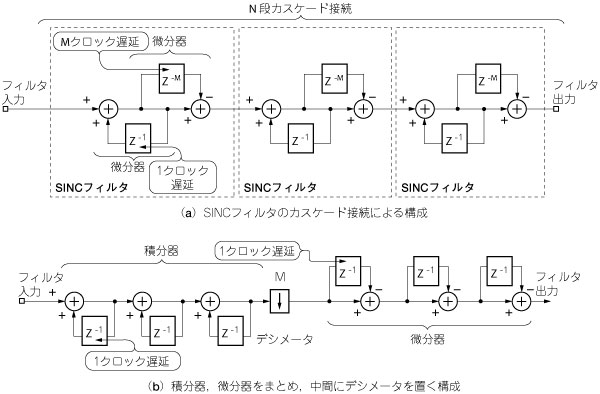

[図14] CICフィルタの構成

[図14] CICフィルタの構成

積分器と微分器を組み合わせたSINCフィルタをカスケードに接続する.下は積分器と微分器をそれぞれまとめ,それらの中間点でデシメーションするもの(積分器のビット幅に注意が必要).

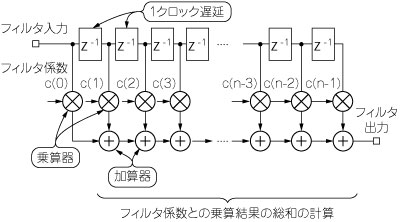

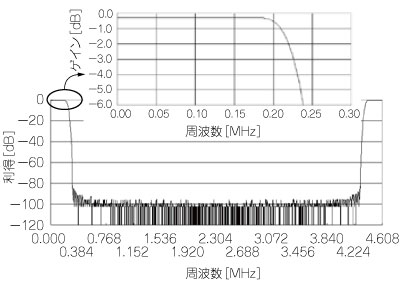

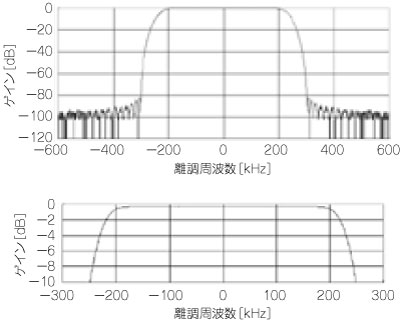

CICフィルタを用いて最初のデシメーションを行った後は,さらにFIRフィルタ(図15)によるローパス・フィルタを通し,不要な成分を除去します.図16は今回使用した192タップのFIRフィルタ(dfir

192d12.vhd)の周波数特性です.通過帯域内でなるべく平坦な特性が得られるよう,最大平坦特性のフィルタとして設計しています(Fs=4.608MHz).

[図15] FIRフィルタの構成

[図16] FIRフィルタの特性例

デシメーションの後段に使用する.通過帯域特性が平坦なFIRフィルタ.このフィルタの減衰特性が受信機としての選択度を実質的に決定する.

最終的にCICフィルタとFIRフィルタを組み合わせた時の総合特性を図17に示します.CICフィルタとFIRフィルタの組み合わせにより,ナイキスト周波数全域に渡ってローパス・フィルタ特性が実現され,目的とする0Hz付近のベースバンド信号以外の信号が効果的に取り除かれていることが分かります.

[図17] CICフィルタとFIRフィルタを接続した場合の総合特性

ナイキスト周波数全域に渡ってローパス・フィルタ特性が実現されている.

このデシメーション・フィルタのローパス・フィルタとしての特性は,受信機の入力周波数に対応させると,受信周波数を中心とするバンドパス・フィルタ特性になります.図18は受信周波数の中心周波数を真ん中に周波数特性を表示したもので,受信機の受信帯域特性としてはこのバンドパス・フィルタとしての表示の方が直感的に分かりやすいと思います.

[図18] 受信機の選択度特性

デシメーション・フィルタのローパス・フィルタ特性を,受信周波数を中心とするハンドパス・フィルタ特性で表示したもの.この特性はFMステレオ・チューナとしてはかなり広帯域.混信が問題になる状況であれば,これより狭帯域のフィルタに入れ替える.

FIRフィルタの係数を格納しているROMの大きさにはまだ余裕がありますので,受信状態に合わせ受信帯域幅を切り替えるよう,複数のFIRフィルタ係数を一つのROMに格納することもできます.受信機基板の上には4ビットのDIPスイッチが実装できますので,フィルタの係数を最大四つまで用意し,このDIPスイッチを用いて受信帯域幅を切り替えるとよいと思います.

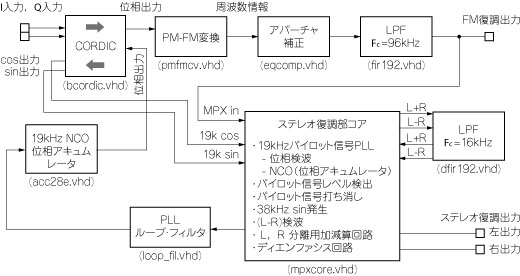

デシメーションによってサンプリング周波数を落とし(Fs=384kHz),それと同時に必要な通過帯域幅を実現できた後は,信号処理の基本クロック周波数を6.144MHzに落とします(一部のブロック,CORDICやFIRフィルタは除く).これは必要にして十分なクロック速度とすることで,回路のゲート数や消費電力を抑えるためです.FM復調とステレオ復調の部分は,一つの大きなブロックにまとめてありますが,その内容は図19に示すような構成になります(dmodmpx.vhd).

[図19] FM復調(検波)とステレオ復調のブロック

CORDICを共有するため,FM復調とステレオ復調のブロックを一つのブロックとした.