インテグリティな技術コラム(6) ―― 転換点は10年前,メモリが非同期型から同期型へ

●「相性問題」は実は設計不良

図4のアドレス線(A0-An)は,すべてのモジュールに共通に接続されています.モジュール上には最大16個のメモリICが搭載されているので,SIMMが4枚の構成の場合,16×4=64個のメモリICが並列に接続されることになります.最大構成ではSIMMが6枚というケースもあり,最大96個のメモリICに接続されていました.当然のことながら,メモリICのアドレス信号は劣悪な波形となりました.当時のメモリは,アドレス信号をクロック同期で取り込む方式ではないので,波形割れがあると,どのタイミングのアドレス信号が有効か分からなくなります.従って,所望のアドレスとは別のアドレスが選択されて,誤動作に至りました.

この不具合は再現性があまりよくなくて,いわゆる「相性問題」として片づけられました.不具合が生じたものとは別のメモリICに置き換えると,問題なく動作する,まさに「相性」のような不具合でした.波形乱れに対する感度やしきい値電圧(Threshold Voltage)のばらつき,内部の遅延時間など,仕様に現れない個体差によって不具合が出たり出なかったりしており,本当の原因がつかめていないので「相性」として片づけていたのです.感情を伴う人と人の間に相性があるのは分かりますが,設計で解決できる問題を「相性」という言葉で片づけるのは,エンジニアとしては恥ずかしいことと思うようになっていただきたいものです.

もう一度,図4のアドレス線の配線を眺めてみます.ボード設計者が,アドレスは4個所にしか配線されていないと錯覚し,「まぁ,何とかなるだろう」と思って4個の負荷のバスとして配線しました.実は,一つの負荷と思った端子には16個のメモリICが空間的な拡がりをもって接続されていました.メモリのアドレス入力の波形は大きく波打ち,アドレスを安定的に取り込めなかったわけです.どのようにすればこの波形乱れを解決できるか,少し考えてみてください.本コラムの稿末に,筆者らが実際の製品に適用した正解の一つを記載します.

●安定動作のために同期化

メモリが高速になり,波形乱れに対して敏感になると,この「相性問題」がもはや「相性」という言葉では片づけられなくなり,抜本的な対策が必要となりました.一般の論理回路と同じように,クロック同期とする新しいアーキテクチャが提案されました.これが同期型メモリ,すなわちSynchronous DRAMの誕生です.クロック同期となったので,波形乱れに対してかなり耐性が強くなりました.その結果,これまでのEDO DRAMでは33MHzだった動作周波数が,66MHz,さらには100MHz,あるいは133MHzと高速化してきました.

高速化によって,また新たな課題が現れました.データ波形が1周期のうちに安定しなくて,それ以上の高速化が困難になってきました.すなわち,データ・バスの限界に至ったわけです.

●整合伝送と小振幅方式を採用

バスを高速化するためには,従来から整合伝送がオーソドックスな解でした.ただ,整合伝送は消費電力の増加を招きます.バス幅が8ビットや16ビットの時代には消費電力の増加もある程度は許容できました.しかし,すでに64ビット・バスの時代になっていました.50Ωの両終端の整合伝送では,ドライバの負荷はその半分の25Ωになるので,電源電圧を3.3Vとすると,消費電力は1ビット当たり200mW程度となります.64ビットでは10W以上となるため,何らかの対策が必要となりました.

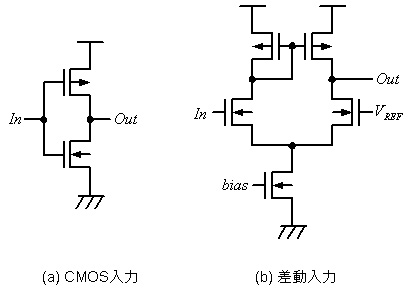

ここで提案されたのが,信号振幅を1/4程度に小さく抑える,いわゆる小振幅方式です.振幅を抑えた結果,消費電力は1/8程度に低減できて,実用上の問題が少なくなりました.また,図5(a)の一般的なCMOSの入力回路では,しきい値電圧の不感帯が1V程度であるため,小振幅に対応できません.そこで,不感帯の小さな図5(b)の差動入力方式を導入しました.これは,差動回路の一方の端子を入力とし,他方の端子に基準電圧を加えるものです.ソース同士を結合した,いわゆる差動対のしきい値電圧のわずかな差が不感帯となるので,信号振幅が小さくなっても問題ありません.

図5 CMOS入力と差動入力

●「波形乱れへの対応」の解答例は...

さて,「相性問題」の対応として,以前に筆者らが実際に採用した方式(1)を紹介します.回路の工夫は,答えを見てしまうと,「なぁーんだ」と言うほど簡単なものです.答えを先に見ずに,まずご自分で考えてみてください.

アドレス線につながる負荷が最大96個にも達するため,波形が乱れます.この波形に対応するために,各SIMMの前に小さなドライバを挿入して波形乱れを最小限に抑えました.ドライバ1段分の遅延が気になりますが,負荷をドライバによって分割すると,重い負荷によるだらだらとした波形なまりが軽減され,ドライバの遅延時間と十分に相殺できます.

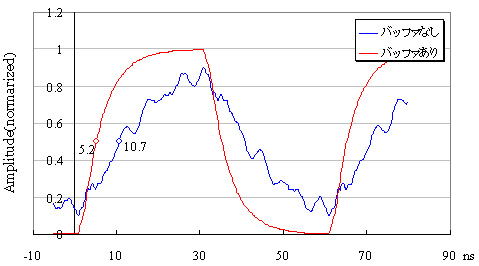

図6にバッファのない元の波形と,遅延時間ゼロのバッファを挿入した場合の波形の違いを解析した結果を示します.バッファありのほうが,遅延時間が5ns程度小さいので,ゲート1段を入れる余裕があります.またこのバッファは,細かい反射を抑制するために,立ち上がり時間を通常より遅い2ns程度に制御しています.本方式を採用したメモリ回路の評価歩留りが100%に達したことは,言うまでもありません.

図6 バッファの有無による波形

参考文献

(1) 碓井 有三;「ドライバ挿入型のSIMM駆動法を開発 分布定数回路の設計手法を駆使」,pp.72-73,日経マイクロデバイス,1997年10月号.

うすい・ゆうぞう

シグナル インテグリティ コンサルタント

http://home.wondernet.ne.jp/~usuiy/