FPGAを使った数値演算回路実現の勘所(2) ―― 乗算器の構成を考える

2.FPGAベンダによる乗算器構築の努力

乗算器を構築する上で,FPGAベンダがユーザに対して与えた最大の恩恵は,何といっても乗算器をハード・マクロとして搭載してくれたことでしょう.

●最新のFPGAではハード・マクロ乗算器が600MHzで動作

かつてはカスタムICやDSPでしか手に入らなかった高速の乗算器が,FPGAで使えるようになりました.これは,FPGAの可能性を飛躍的に向上させたといえます.

ハード・マクロが搭載されていなかったころのFPGAでは,乗算器はすべて,組み合わせ論理を実現するための論理ブロックを費やして構築していました.これは速度の面で不利なだけでなく,ハードウェア・リソースの有効活用の面でもかなり不利でした.加算器を1次元的な回路とすれば,乗算器は2次元的な構成の回路です.ビット幅が増えるとたちまち大きな回路となり,論理ブロックを大量消費してしまうため,高価な大規模デバイスを使わざるをえないという状況があちこちで見られました.これを解決してくれたFPGAベンダには感謝したいと思います.

その後,製造プロセスの進化により,乗算器の能力はさらに高まります.米国Xilinx社のFPGAを例にとれば,Virtex-6の「DSP48E1」では600MHz,Spartan-6の「DSP48A1」では320MHzの動作周波数がうたわれています(「DSP48~」は乗算機能を含むハード・マクロで,信号処理に有利なように「乗算+加算」の機能を備えている).もちろん性能は最大値を表わし,この性能を出すには若干の作法に従う必要があります.

●論理ブロックの内部にも乗算器向けの工夫が...

上述のように,かつてのFPGAではハード・マクロを使わずに,論理ブロックを組み合わせて乗算器を実現していました.もちろん現在でも,そのように実現することは可能ですし,状況によってはそれが必要になります.例えば,選択したデバイスのハード・マクロ乗算器を使い切ってしまったが,もう一つ乗算器を載せたい場合とか,ハード・マクロ乗算器を使うほどではない小規模の乗算器を載せたい場合,あるいはリアルタイムで乗算する必要はないので,シーケンシャルに乗算して回路規模をケチりたい場合など,いろいろなケースが考えられます.

では,論理ブロックを使って乗算器を実現する場合を想定して,FPGAにはどのような工夫がなされているのでしょう.Xilinx社のSpartan-3を見ると,なかなか心憎い構造となっていることが分かります.

まず,図3(c)を再度参照してください.この構成はまさに論理ブロックによる実現をイメージしたもので,部分積を求めたあとに加算器がツリー上に配置されていることが分かります.Spartan-3では,この「部分積→加算器1段目」の構成に工夫があります.

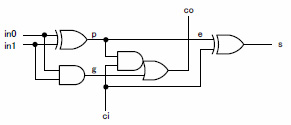

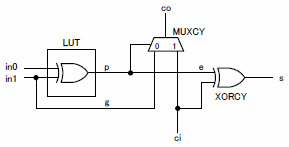

図7(a)には,本連載の第1回でお話しした加算器の1ビット当たりの機能を原理で示します.これをSpartan-3に実装した場合,図7(b)のようになります.ここに部分積生成のANDを入力側に2個配置してみると,図7(c)となります.同一けたに部分積を生成する2個のANDということになります.

(a) 1ビット当たりのアダー機能

(b) Spartan-3における実装

(c) 部分積生成のANDの追加

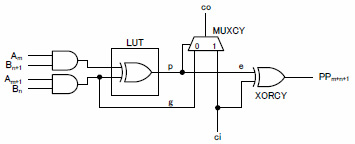

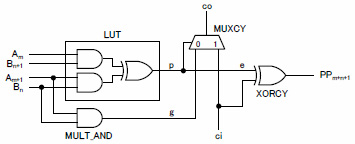

(d) 最適化後の実装

図7 Spartan-3の論理ブロックの工夫

これをSpartan-3では,図7(d)のように最適化して実装しています.二つのANDをLUT内部に同居させてしまうのです.MUXCYの0側の入力項をLUT内部から引き出せればよいのですが,Spartan-3のLUTは4入力1出力と決まっているので,部分積生成をLUT内で行ってしまった場合,図7(c)における"g"の項を取り出すことができません.そこで,LUTの外にANDを1個用意し,LUT内のANDのうちの1個を複製しています.LUTと並列に複製したことで,ゲート段数を増やすことなくLUT内から"g"の項を取り出すのと同じ効果を得ています.このANDはMULT_ANDと呼ばれています.

さて,これにより何が起きるのかというと,部分積生成と1段目の加算器までを一つの論理ブロックに割り当てられるのです.「論理ブロックが1段減るだけじゃないの?」などと侮ってはいけません.乗算器で最も多くの項が発生するのが部分積の段階ですし,加算器のツリーを考えれば最も加算器の数が多いのは1段目の加算器です.例えば32ビットの入力を想定すれば,1段目の加算器は16個必要になり,その後,8個,4個,2個,1個という具合に続くので,合計で31個の加算器が必要です.つまり,部分積生成と1段目の加算器が合体して一つの論理ブロックに入るということは,加算器の数を半減させることになり,回路規模の節約に大きく貢献します.その上,信号遅延,あるいはレイテンシも減るので,その効果は絶大です.実によく考えられています.

8ビットの符号なし乗算を例にとれば,この機能を利用すると63個のLUTで構成できます.部分積を別に生成した場合は,127個のLUTが必要になります(筆者推定).部分積生成用のLUT分が別途必要となり,回路規模が2倍になってしまうので,この差は大きいといえます.