FPGAを使った数値演算回路実現の勘所(2) ―― 乗算器の構成を考える

●リアルタイム処理が不要で回路規模をケチりたい場合

最後に,乗算を毎クロック行うのではなく,一定時間内に行えば済むような仕様の場合に,ロジック・セルを節約して使用する方法を紹介します.もちろん,ハード・マクロ乗算器は必要ありません.すでに説明したとおり,乗算は部分積を求めたあとにけたをそろえてひたすら加算する,という機能があればよいので,部分積のAND演算もそのあとの加算も並列に行わなければならないわけではなく,シーケンシャルに順次演算してもかまいません.並列演算が使用されるのは,演算能力を上げたい場合なのです.のんびり演算してもかまわない場合は,リソースをケチってみることをお勧めします.

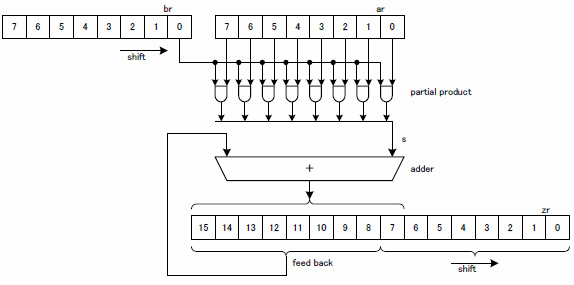

図10(a)に設計例のブロック図を示します.

(a) シーケンスによる乗算 Aタイプ

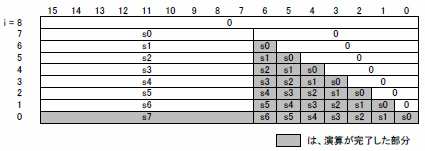

(b) レジスタzrの内容

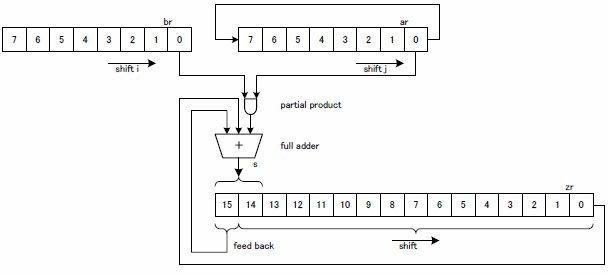

(c) シーケンスによる乗算 Bタイプ

図10 シーケンシャルに順次演算してリソースをケチる

符号なし8ビット×符号なし8ビットの乗算において,8サイクルのシーケンスによって1回分の乗算を行います.仕組みは至って簡単です.レジスタar,brはそれぞれ被乗数,乗数を格納するためのものです.演算開始でこのレジスタに値が格納されます.zrは積を格納するレジスタですが,一時レジスタと兼用し,演算開始で0に初期化されます.1クロック当たりの演算は,以下のとおりです.

zr[15:7]=zr[15:8]+a×b[i] (8)

これは,被乗数aに1ビット分の乗数b[i]を乗じて部分積を生成し,これをzrの値と加算するというものです.b[i]をforループで回しながらa×b[i]を加算していくイメージです.加算によるキャリは上位に出るので,iは0から(下位から)開始します.zr[15:8]を前シーケンスの演算結果として取り出し,部分積と加算した結果をzr[15:7]に戻します.この際,同時にzr[7:0]は1ビット分ダウン・シフトして,前シーケンスと現シーケンスで1けたずれた状況を作り出します.

図10(b)にはzrの内容をシーケンスごとに示しています.図1(b)に示した方法で加算を1行ずつ行ったと考えればよいでしょう.回路規模については,並列演算による乗算器をn2とすれば,この回路はnとなります.ただし,シーケンサが別途必要となります.

これに対して,図1(a)に示した方法で加算を1行ずつ行うこともできます.変数iとjでforループのネスティングを行って,a[i]×b[j]を加算していくと考えればよいでしょう.設計例のブロック図を図10(c)に示します.この場合,演算に必要なリソースはAND1個とフル・アダー1個になり,極限まで回路規模を抑えたことになります.しかし,レジスタに必要なビット数が先の設計例と変わらないので,組み合わせ論理とレジスタが1:1で対応しているFPGAの場合は,回路規模の節約には効果がありません.

●IPコア生成ツールの設定方法

最後に,以上の回路をXilinx社のIPコア生成ツール「Core Generator」を使用して実現する方法を付け加えておきます.ここで使用するのはMultiplier Version 11.0です.

ハード・マクロ乗算器でけたが不足する場合に,ロジック・セルで回路を付け足したいときは,以下のように設定します.

Multiplier Type=Parallel Multiplier

Multiplier Construction=Use Mults

Optimization Options=Area Optimized

ここで,以下のようにすればすべてハード・マクロ乗算器で生成されます.

Optimization Options=Speed Optimized

ただし,複数のハード・マクロ乗算器の出力を取りまとめるためのロジック・セルは必要になります.

すべてロジック・セルで乗算器を構成したいときは,以下のように設定します.

Multiplier Type=Parallel Multiplier

Multiplier Construction=Use LUTs

ハード・マクロ乗算器1個に複数の乗算器を詰め込む場合や,シーケンシャルな乗算をロジック・セルで行う場合については,少なくともMultiplier Version 11.0では対応していません.しかし,それほど面倒な回路ではないので,自力で設計してみてください.特にシーケンシャルな乗算回路は,一度パラメタライズされたソースを作成しておけば,何度でも使い回しできるので,便利です.

* * *

FPGAには高性能を実現するために,普段意識していないような仕掛けが隠されています(もちろん,データ・シートやアプリケーション・ノートに説明されているので,本当に隠されているわけではないが...).知らないところで恩恵にあずかっていたりもするので,ちょっと気をつけてみると面白い発見がありますし,うまい使い方が見つかることもあります.「常々勉強を怠ってはいけません」というところでしょうか.

●参考文献

(1) Xilinx社;Spartan-3ジェネレーションFPGAユーザーガイド.

(2) 鈴木 昌治;ディジタル数値演算回路の実用設計,CQ出版,2006年.

すずき・しょうじ