FPGAを使った数値演算回路実現の勘所(2) ―― 乗算器の構成を考える

3.乗算器に対するケース別の対処方法

以下では,実際の設計で起こりうる三つのケースについて,乗算器を構成する際の考え方を示します.

●ハード・マクロ乗算器ではけたが不足する場合

まず,ハード・マクロ乗算器を使う際に,けたが足りない場合を考えます.

Spartan-3を例にとると,ハード・マクロ乗算器(Xilinx社ではEmbedded Multiplierと呼んでいる)の入力は,A,B共に符号付き18ビットです.いろいろなアプリケーションにおいて,ぴったりこのビット幅に合致する場合はまれだと考えられます.符号付き18ビットの回路に包含される場合は悩む必要はありません.また,符号付き32ビットの乗算であれば,ハード・マクロ乗算器を複数使用しても納得できるでしょう.

しかし,符号付き19ビットや符号なし18ビットなどの場合は,もったいなくてハード・マクロ乗算器を複数使用する気になりません.デバイス内のハード・マクロ乗算器がたっぷり余っていれば話は別ですが,往々にしてリソースは不足するものです.そのような場合,ハード・マクロ乗算器と論理ブロックの併用によるハイブリッド型の回路で対処することになります.

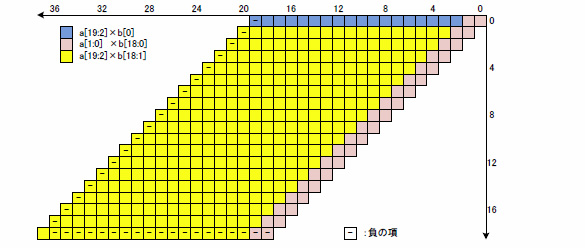

符号付き20ビット×符号付き19ビットの場合の部分積の配列図を図8(a)に示します.

(a) 符号付き20ビット×符号付き19ビット部分積配列

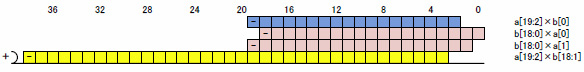

(b) 符号付き20ビット×符号付き19ビットまとめ加算

図8 ハード・マクロ乗算器とロジック・セル乗算器を併用

ここで,黄色で塗りつぶした部分が「符号付き18ビット×符号付き18ビット」の乗算になっていることに注目してください.乗算の大きさおよび負となる項の位置がその並びになっています.この部分をハード・マクロ乗算器に割り当て,それ以外の部分をロジック・セルに割り当てることで,ハード・マクロ乗算器の浪費と論理ブロックの節約を図るわけです.各部分の乗算の担当領域は,以下のようになります.

a[19:2]×b[0] ロジック・セル乗算器 青領域

a[1:0]×b[18:0] ロジック・セル乗算器 赤領域

a[19:2]×b[18:1] ハード・マクロ乗算器 黄領域

赤領域は部分積生成と1個の加算器で実現できるので,先ほどの説明のとおり1段のロジック・セルで実現できます.それぞれの領域ごとに求めた結果を最後にまとめて加算すれば,符号付き20ビット×符号付き19ビットの乗算が完成します.その様子を図8(b)に示します.ビットの重みに応じてけたをそろえることと,いずれも符号付きの値になることに注意してください.なお,青領域と赤領域の加算は,ハード・マクロ乗算と並列に処理できるので,最終的な加算のステップでは2変数の加算となります.

●ハード・マクロの数が足りない場合

※ 2010年7月22日に公開した本記事の「●ハード・マクロの数が足りない場合」の内容について,説明に一部誤りがありました.お詫びして訂正いたします(現在は修正されています).

次に,ハード・マクロ乗算器の数が足りない場合を考えます.

既に説明したとおりロジック・セルで乗算器を構成できるので,リソースが許すのであれば,ロジック・セルで乗算器を実現するのが確実な方法です.ですが,「符号なし5ビット×符号なし5ビットの乗算がたくさん欲しいのだが,ハード・マクロ乗算器では数が足りないし,5ビット同士の乗算に18ビットのハード・マクロ乗算器を1個使ってしまうのはもったいない」というような経験はありませんか? 条件が合えば,このようなときには裏技があります.1個の18ビットのハード・マクロ乗算器に2個の乗算機能を割り当ててしまうのです.

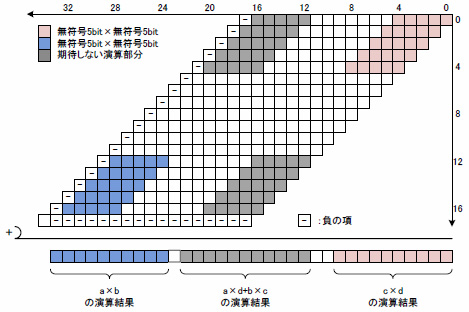

符号なし5ビット×符号なし5ビットを割り当てた部分積の配列と乗算結果を取り出す出力けたの例を図9(a)に示します.

(a) 符号なし5ビット×符号なし5ビットを2個割り当てた部分積配列

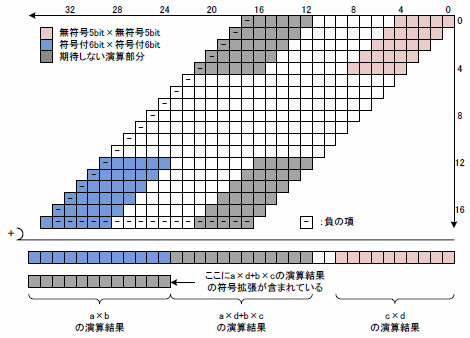

(b) 符号なし5ビット×符号なし5ビット,符号付き6ビット×符号付き6ビットを1個ずつ割り当てた部分積配列

図9 1個のハード・マクロ乗算器に複数の乗算機能を割り当てる

ハード・マクロ乗算器に入力する二つの変数のそれぞれにおいて,上位側と下位側に別々の変数を割り当て,出力から二つの乗算結果を得ようという考え方です.要は二つの乗算結果が出力でオーバラップしなければよいだけですが,若干の工夫が必要です.図9(a)において,上位側で行う乗算をa×b,下位側で行う乗算をc×dとします.一つの乗算器の中で行われる演算は以下のとおりとなります.

(a×2n+c)×(b×2n+d)=a×b×22n+(a×d+b×c)×2n+c×d (7)

aとbに2nを乗じているのは,上位へシフトしたけた位置に割り当てたことを示しています.結果の中から欲しいのは,a×b×22nとc×dなのですが,(a×d+b×c)×2nという副産物が生じるので,この3項が出力でオーバラップしないように,入力側で割り当てるけたを調整する必要があるのです.要するに,上式におけるn(上位側で乗ずる変数a,bのシフト量)を適切に決めてやることです.

符号付き乗算を割り当てる場合には,さらなる注意が必要です.図9(b)には符号なし5ビット×符号なし5ビット,符号付き6ビット×符号付き6ビットの二つの乗算器を割り当てた例を示します.符号付き18ビット×符号付き18ビットの乗算機能を利用しようという考えで,入力変数aとbを符号付きとして18ビットの最上位側に割り当てます.しかしこの例では,上位側から符号なし乗算の結果を引き出したときとは違い,正しい結果を引き出すことができません.なぜなら,(a×d+b×c)×2nという副産物が悪さをするのです. 図9(b)からも明らかですが,(a×d+b×c)という項は二つの符号付きと符号なしの乗算結果の和なので,当然,符号付きになります.従って,この項が負となった場合には,符号である「1」が最上位まで拡張されて2の補数における「-1」となったうえで,a×b×22nの項とオーバラップしてしまうのです.この問題は,(a×d+b×c)の符号ビット(最上位)をa×bに加算することで解決できます.ただし,乗算器の外部で行う必要があるため,それなりのリソースが必要となります.

以上の方法については,二つの乗算器が同じ仕様である必要はありませんし,入力変数が同じビット幅である必要もありませんが,仕様によっては効率的に割り当てられない場合もあるので,注意してください.

また,3個以上の乗算を1個の乗算器に割り当てることも原理的には可能です.しかし,本来結果として欲しい乗算項よりも,不要な副産物の項が圧倒的に多くなってしまい,それらとけたを共有しないようにした場合,無用なけたが支配的になってしまいます.少なくとも18ビット×18ビットの中に押し込むのは現実的ではないでしょう.不要な部分積はマスクしてしまう機能があるとけたが有効に使えて便利なのですが,それはぜいたくというものでしょうか.

以上,小粒の乗算器がたくさん必要なときに,検討してみる価値のある話でした.