USB 3.0規格のFAQ(3) ―― SuperSpeed USBのテストはどのように行うか?

Q.USB 3.0の測定に必要なオシロスコープの周波数帯域は?

A.最低でも12.5GHz周波数帯域を推奨する.

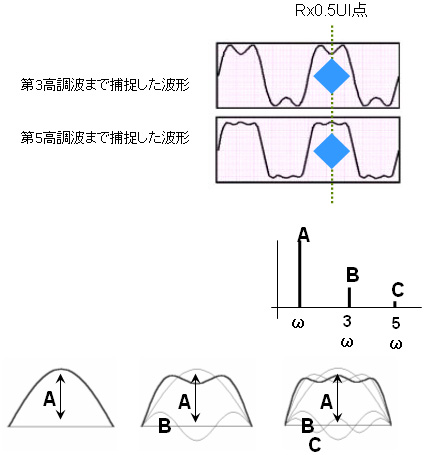

基本波と奇数高調波で構成される方形波では第5高調波の捕捉が必要,という考え方を基にしています.USB 3.0などで採用されているNRZ(Non Return to Zero)信号の基本波はデータ・レートの1/2となり,基本波は2.5GHzですから,第5高調波は12.5GHzとなります.第3高調波までの捕捉ではUIの中央で波形が凹み,マスク・テストにおいてマージンが低下しているように判断される可能性があります(図10).ただし,実際は信号の立ち上がり時間にも依存します.

図10 捕捉高調波とマスク・テスト

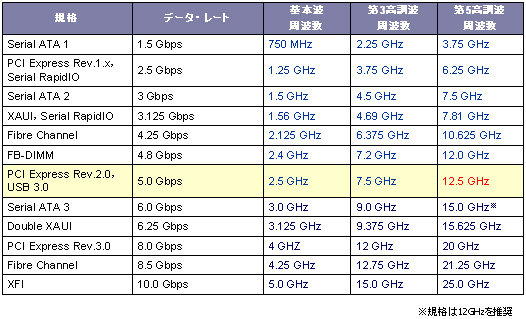

参考までに,主な高速シリアル・インタフェースの規格と第5高調波周波数を表1に示します.

表1 主な規格と第5高調波周波数

Q.USB 3.0を使用したデバイスには,どのような実現方法があるか?

A.ASIC,ASSP,さらにFPGAと外付けPHYチップを組み合わせる方法が考えられる.

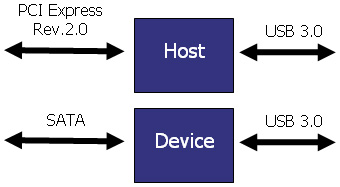

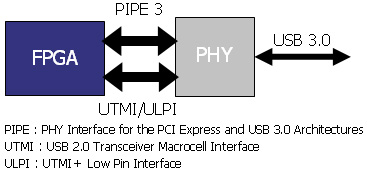

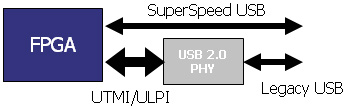

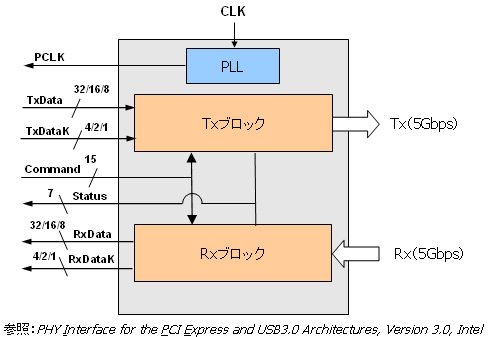

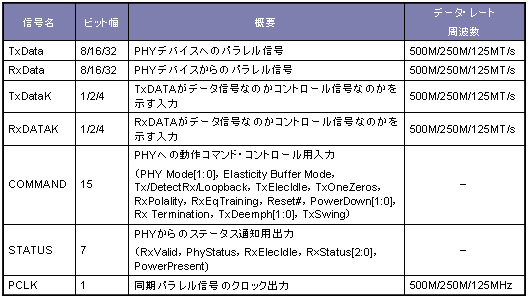

図11を参照してください.FPGAと外付けPHYチップを組み合わせる場合,MAC(Media Access Layer)までをFPGAに埋め込みます.そして,USB 3.0はPIPE 3(Phy Interface for the PCI Express and USB 3.0 Architectures Rev. 3.0)<リンク>で,USB 2.0はUTMI(USB 2.0 Transceiver Macrocell Interface)またはULPI(UTMI+Low Pin Interface)で外付けPHYチップと接続します.図12にPIPE 3の信号を示します.TxData/TxDataK,RxData/RxDataKのバス幅は,バス周波数(125MHz,250MHz,500MHz)により使い分けます.5Gbpsを超える高速トランシーバを内蔵したFPGAがすでにPCI ExpressやSerial ATAに対応している点から,USB 3.0も早期にサポートする可能性があります.ただしこの場合,レガシのUSB 2.0についてはPHYチップを外付けすることになります.

(a) ホスト・コントローラ/ブリッジLSI(1チップですべて実現)

(b) FPGA+外付けPHYチップ(FPGAはMACまで,比較的低価格)

(c) FPGA(高性能トランシーバ内蔵のFPGAで実現,レガシUSBは外付けPHYチップ)

(d) ASIC(1チップですべて実現)

図11 実現方法

(a) 信号の構成

(b) 信号の概要(電気的な仕様は規定されていない)

図12 PIPE 3インターフェース