USB 3.0規格のFAQ(3) ―― SuperSpeed USBのテストはどのように行うか?

Q.認証テストでは何を測定するのか?

A.トランスミッタはアイの高さとジッタを測定し,レシーバはジッタ耐性テストを行う.

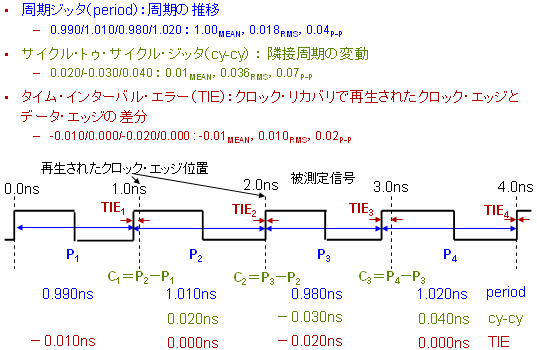

データ・レートの高速化に伴い,ジッタの問題がクリティカルになってきています.高速シリアル・インターフェースのジッタは,クロック・リカバリ回路で再生されたクロックと実際のデータ・エッジの間のずれ(TIE:Time Interval Error)によって評価されます(図1).TIEを計測するためには再生されたクロックが必要ですが,クロック・リカバリ回路により再生されたクロックは,チップ内部でしか得られません.そのため,認証テストの測定の際には,1M-UI(ユニット・インターバル)のデータをオシロスコープに取り込み,ソフトウェアでクロック・リカバリの機能をエミュレートする方法をとっています.

図1 シリアル・インターフェースのジッタはTIE (Time Interval Error )

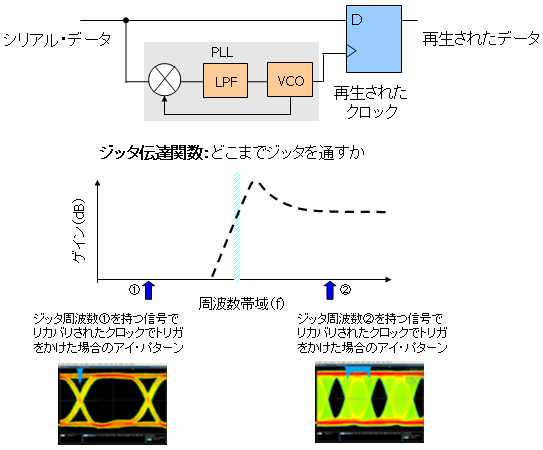

クロック・リカバリ回路のPLLは,ジッタが持つ周波数成分と振幅(揺らぎの大きさ)により,以下のように変わります(図2).

- ロールオフ周波数以下のジッタ成分にはPLLが追従するので,ジッタが吸収される

- ロールオフ周波数以上のジッタ成分にはPLLが追従できないため,ジッタが吸収されない

- ピーキングがあると逆にジッタは増加する

- 過渡領域におけるジッタの吸収度合いは,ジッタの周波数と振幅に依存する

そのため,測定に使用されるPLLの特性を統一する必要があります.USB 3.0では10MHz帯域の2次PLLを使用します.2次PLLとは,ジッタ伝達関数として40dB/decの減衰特性を持つPLLです.

図2 クロック・リカバリの特性

ジッタについては,レシーバ端のすべてのジッタを評価するわけではなく,クロック・リカバリ回路が吸収できないジッタだけを評価する,ということを理解しておく必要があります.実際に受信に影響を与えるのは,PLLで吸収できなかったり増幅されたりするジッタなのです.

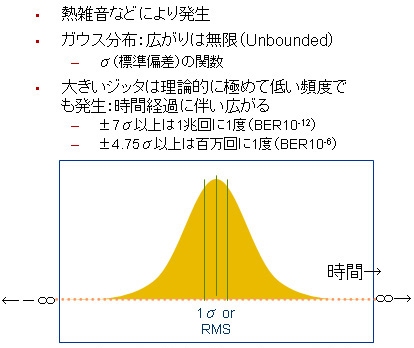

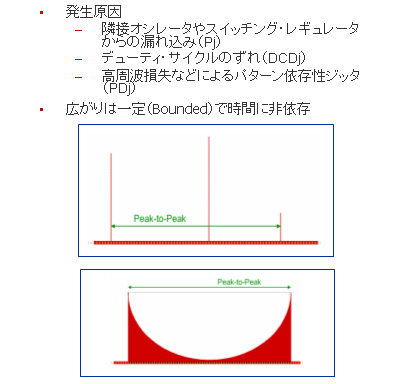

さらに,ジッタには図3のように性質の異なる2種類,すなわち「ランダム・ジッタ」と「デターミニスティック(決定性)ジッタ」が存在し,これらが合成されて表に現れています.ランダム・ジッタは回路中の熱雑音やフリッカ・ノイズ,ショット・ノイズなどが原因で発生します.発生頻度は低いものの,理論上-∞~+∞のジッタが存在します(Unbounded).一方,デターミニスティック・ジッタは隣接オシレータやスイッチング電源からの発振の漏れによるジッタ,および伝送路の周波数特性によるパターンに依存したジッタなどであり,ジッタの振れ方はある一定の範囲にとどまります(Bounded).

(a) ランダム・ジッタ(Rj)

(b) デターミニスティック・ジッタ(Dj)

図3 高速シリアル・インターフェースでは,性質の異なるジッタ成分を分けて把握する必要がある

ランダム・ジッタの分布は統計で知られる正規分布(ガウス分布)となり,平均的なばらつきの幅をあらわすσ(標準偏差)の関数で表現されます.大きな揺らぎの発生頻度は低いのですが,長期間で見た場合,その中で発生する可能性があります.例えば±7σを超えるジッタの発生頻度は1兆回(1012)に1度となります.このような頻度は極めて低く感じられますが,5Gbpsのデータ・レートで見ると200秒(=1/(5×109)×1012),すなわち3分20秒に1度発生する頻度です.もしこの大きなジッタが正しくビットを捕捉できない要因となり,エラーを引き起こすとすれば,この発生頻度はそのままビット誤り率(BER:Bit Error Rate)を意味することになります.

上述の1兆回に1度という発生頻度は高速シリアル・インターフェースで確保されるべきビット誤り率の一般的な基準となっており,「BER10-12」と表現されます.一方,デターミニスティック・ジッタの大きさは時間に依存しませんが,ランダム・ジッタに対する余裕度を低下させます.

このように性質の異なる2種類のジッタが合成されているため,最近の高速インターフェースのトランスミッタの測定では,ランダム・ジッタとデターミニスティック・ジッタ,さらにランダム・ジッタに依存する長期間(BER10-12)のジッタ量(トータル・ジッタと呼ばれる)を評価するという考え方が定着しています.USB 3.0でもこの考え方を採用しています.

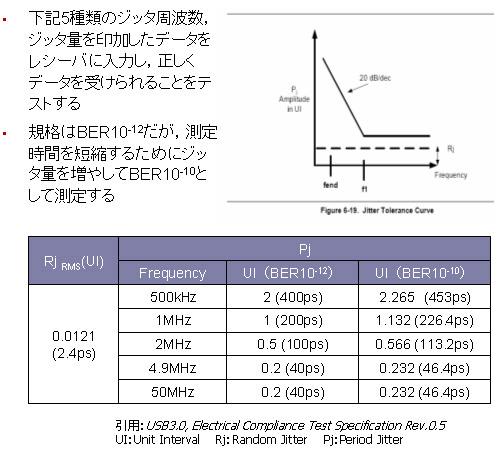

レシーバ側では,クロック・リカバリの特性やデータを再生する回路のジッタ余裕度もキーとなります.そのため,ジッタ耐性テストが行われます.ジッタ耐性テストとは,図4のように決まった周波数のジッタを決まった量(ジッタ振幅)印加したデータを入力しても,レシーバが正しくデータを受信できるかどうかを確認する作業です.Serial ATAやDisplayPortなどの評価でも必須項目として採用されています.

なお,USB 3.0にはInformativeとNormativeの2種類のテストが規定されています.Informativeは参考測定用で,Normativeが認証テストの必須項目です.

図4 レシーバ・テスト(ジッタ耐性テスト)