フラッシュFPGA本家のActelが65nm製品を開発中,ダイナミック電力を一気に削減へ ―― 携帯機器搭載を目指すフラッシュFPGAの製品動向

米国Actel社は,低消費電力を特徴とするフラッシュ・ベースのFPGAを出荷している.これは,SRAMセルではなくフラッシュROMセルを使ってプログラミングを行うFPGAである.例えば3万ゲート品のスタティック消費電力は標準で5μWと低い.

ここでは同社の低消費電力技術と今後の製品動向について,同社 President & CEOのJohn C. East氏と,Vice President, Marketing and Business DevelopmentのRich Kapusta氏に話を聞いた(写真1).

[写真1] Actel社 President & CEOのJohn C. East氏(左)と,同社Vice President, Marketing and Business DevelopmentのRich Kapusta氏(右)

――Actel社のロゴ・マークの中に"POWER MATTERS"の文字が加わった.消費電力の問題を大きな課題と認識しているのか.

John C. East氏 地球温暖化をはじめとして,エネルギの過剰な使用が多くのトラブルを引き起こしている.新聞で「日本の漁師がストライキを行った」というニュースを読んだ.石油の高騰が経済に影響を与えている例だ.石油の半分は自動車に,残りの半分は発電に使われている.そして電力消費量の急激な増加の原因となっているのはコンピュータと通信設備だ.当社は,エネルギ消費を抑える"グリーン"な半導体製品を設計して,エネルギの節約に対して貢献していく.

――Actel社は,低消費電力のFPGAを相次いで市場に投入している.どのような技術によって低消費電力化を実現しているのか?

John C. East氏 競合する技術と比較する場合,比較の対象は2種類ある.一つ目は低消費電力を標榜するSRAMベースのFPGA,二つ目はCPLDである.

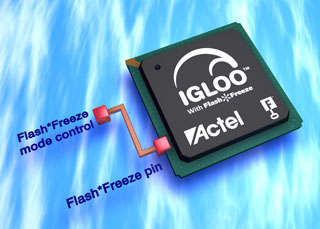

SRAMセルを使ってプログラミングを行うFPGAは,65nmなどの微細なプロセスで製造されることが多い.そして,SRAMセルは六つのトランジスタから構成される.そのため,1セル当たりのリーク電流が大きく,プロセスが微細になるほどこれが増加する.一方,Actel社のフラッシュ・ベースFPGAであるIGLOOファミリ(写真2)は130nmプロセスで製造している.フラッシュROMセルは一つのフローティング・ゲートで構成される.そのため,セル当たりのリーク電流はごくわずか.このように,SRAMベースのFPGAには,スタティック消費電力が大きくなるという問題がある.

[写真2] IGLOOファミリの外観

CPLDについては,一般に180nm程度のプロセスで製造される.適切なアーキテクチャを採用すればスタティック消費電力は下がるはずだが,CPLDベンダはそれほどスタティック消費電力の低減に力を入れていないようだ.ただし,CPLDで問題となるのはスタティック消費電力よりもダイナミック消費電力.ダイナミック消費電力P,キャパシタンスC,電圧V,周波数fの間にはP=CV2fの関係がある.180nmプロセスを採用するCPLDのコア電圧は1.8V,130nmプロセスのIGLOOのコア電圧は1.2V.これでダイナミック消費電力に2.25倍の差が出る.つまり,CPLDには,ダイナミック消費電力が大きくなるという問題がある.

Rich Kapusta氏 当社は,パワー・ドリブンの(消費電力を考慮して最適化する)配置配線ツールや論理合成ツールを用意している.こうしたツールを使うことにより,ダイナミック消費電力を引き下げられる.また,内部状態を保ちつつクロックを止める「Flash*Freeze」と呼ぶ低消費電力モードを用意している.これを利用すると,スタティック消費電力を引き下げることができる.

――FPGAには集積度向上や低コスト化の要求もある.フラッシュROM技術を採用しているが,プロセスの微細化には対応していけるのか?

John C. East氏 答えはYesだ.現在,低リーク電流の65nmプロセスを利用したFPGA製品の開発を進めている.シミュレーションによって,スタティック消費電力を抑えつつ,ダイナミック消費電力も大幅に下がることを確認している.65nmプロセスで製造するようになっても,消費電力について,フラッシュ・ベースFPGAの優位は変わらない.

――フローティング・ゲートを微細プロセスで製造することになるが,信頼性の確保について問題はないのか.

John C. East氏 テスト・マスクは作っており,問題なくいけると考えている.世の中には65nmプロセスで製造されたフラッシュROMが既に存在している.当社のFPGAについても,十分なリテンション(データ保持)が得られると思っている.

――Actel社はパッケージの小型化にも力を入れている.

John C. East氏 4mm×4mmの81ピンCSP(Chip Size Package)を用意している.これは,他社のFPGAにはない最小のパッケージだ.

――低消費電力と小型パッケージを武器に日本市場を攻略していくのか.

John C. East氏 いや,それだけではダメだと考えている.アジアや日本の市場では,さらに低コスト化が要求される.具体的には1ドル以下の価格だ.これまでは提供してこなかったが,今後1年の間に,1ドル以下を狙ったデバイスを製品化する.発表前なのでまだ詳しいことは説明できない.

――それは,先ほど説明していただいた65nmプロセスで製造する製品のことか?

John C. East氏 その質問には答えられない.

関連記事

・Actel,携帯機器向け低消費電力フラッシュFPGAを発売

・Actel,システム・ゲート数が15,000,スタティック消費電力が5μWのフラッシュFPGAを発売

・Actel,I/O端子の数を増やした低消費電力フラッシュFPGAを発売

・Actel,4mm×4mmと小さいFPGA用のパッケージを用意

・Actel,低消費電力フラッシュFPGAの開発キットを発売