ギガビット高速信号伝送を理解するための基礎知識(後編) ―― 特性インピーダンスからコーディング方式,SerDes回路,イコライザ補償まで

●AC結合ではランレングスやDCバランスに配慮したコーディング方式が必要

高速通信のアプリケーションでは,伝送路中にACカップリング・コンデンサを配置し,直流成分のオフセット電圧をキャンセルする方法が多く採用されています.コンデンサを挟むと直流成分が通らないため,ランレングス('0'や'1'の連続数)やDCバランスを配慮したデータ・コーディングが必要になります.

クロック信号はHighとLowの繰り返しの時間が短く,また同じ時間であればACカップリング(AC結合)を採用してもHigh側とLow側のエネルギーが同じ(DCバランスが取れている)ため,ACカップリング後の信号はDCオフセット電圧が変わるだけで,信号伝送において問題は起こりません.これに対してRaw(生)データの通信では,HighとLowの個数や繰り返しの時間を規定できません.ある時はHighが続き,ある時はLowの時間がHighよりもずいぶん長いかもしれません.

そのため,データ通信のACカップリングでは,ランレングスを制限するとともに,データの'0'の数と'1'の数の差を一定以内とするか,後述するデータ・コーディングにより'0'の数と'1'の数に差がないような制御(DCバランス・コーディング)を行います.

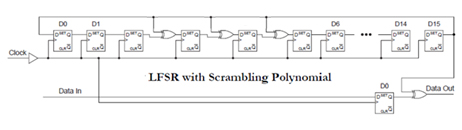

1990年代の複数の高速通信規格は,データの遷移を均一化する一つの手段としてPRBS(Pseudo Random Bit Sequence)によるスクランブル(疑似スクランブル)のデータ・コーディングを採用していました(図13).

図13 スクランブル回路例

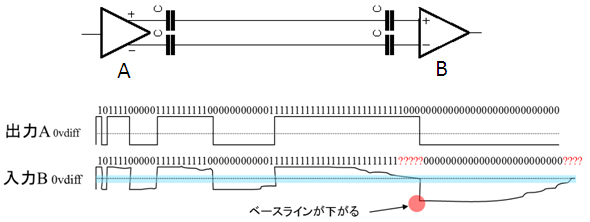

AC結合を使用すると,特殊なデータ・パターンにおいて均等な'0'と'1'の数を意味するDCバランスが大きく崩れ,ベースライン・ワンダ(ベースラインのDC成分のズレ)が起こり,データ・エラーが発生する場合がありました(図14).

図14 ACカップリング(ランレングスが長いデータの挙動)

最近の汎用SerDesデバイスや新しい高速通信規格などでは,ACカップリングのこの問題を回避するため,8B10Bコーディング(8ビットのデータを10ビットのシンボルに変換して伝送する方式)やDCバランス・ビットの追加などを行うようになっています.

●パラレル・バスをシリアル化して高速に伝送

基板上のデバイス間のデータ送受信では,アドレス・バスとデータ・バス(または時間軸で多重化したアドレス・データ・バス)が使用されます.以前は,バス幅を広げたり,リファレンス・クロックの周波数を引き上げることで,帯域を増やしていました.初期の頃の「8ビットから16ビットへ」,「8MHzから32MHzへ」といった改善は容易でしたが,「64ビットから128ビットへ」,「64MHzから128MHzへ」といった変更では,バス信号の基板設計や,クロックとデータのスキュー設計が非常に難しくなりました.基板間をまたぐパラレル・バスの伝送や外部との通信が必要になると,設計はさらに困難になりました.

このような問題を解消するために使用されるようになった技術が「シリアライザ/デシリアライザ(いわゆるSerDes)」です.SerDesは,多ビット・バスのデータとリファレンス・クロックの信号を1本もしくは数本にシリアル化し,高速・長距離伝送を実現する方式です.さまざまなSerDesデバイスが出荷されており,また各種の高速伝送規格でも同じような機能が採用されています.

以下に,代表的なSerDesの種類と機能を紹介します.

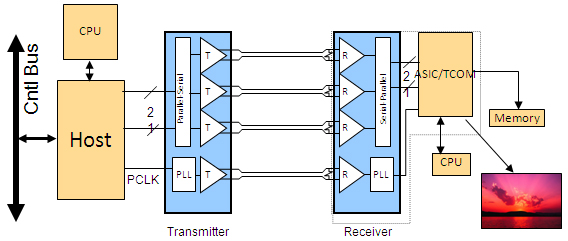

1) LVDS SerDes

LVDS SerDesは1990年代半ばに登場しました.LVDS信号の1対に対してパラレス・バスの7ビットを割り当ててシリアル化し,LVDS物理層を使用して高速伝送する方式です.クロックは別ラインの並送です(図15).

図15 LVDS SerDes

パラレル・バスと似た構成のため,高速化によるデータとクロックのスキューの仕様(RSKM:Receiver Input Skew Margin)の制限があり,高速化・長距離伝送には限界があります.しかし,伝送距離の短い筐体内やバス・クロックが100MHz程度までの短距離伝送については,低コストで容易にパラレル・バスを変換できるため,民生品ではディジタル・テレビやプリンタ,ノート・パソコン,パソコン・モニタ内部のインターフェースとして標準的に使用されています.ディスプレイ系のシステムでは,このLVDS SerDesの機能含めて,略称で「LVDS」と呼んでいます.

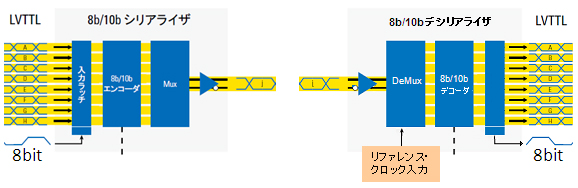

2) 8B10B SerDes

8B10B SerDes(8b/10b SerDes)は,1983年に米国IBM社のエンジニアたちによって発表された方式です(図16).HPC(High Performance Computing)やデータ通信において,高速・長距離通信で標準的に使用されています.8ビットを10ビットに変換するため,20%のロスがあると説明される場合が多いようです.しかしコーディング上,20%以下の低い周波数成分がなく,自動の帯域制限(最低周波数 > ビット・レート×20%)があるため,高周波帯域での減衰の大きいGbpsクラスの高速伝送や長い伝送路において低周波の振幅を自動的に抑え,ISI(Inter-symbol Interference;シンボル間干渉)ジッタを低減する効果を持っています.

図16 8B10B SerDes

8B10B SerDesは,DCバランスのとれたコーディング方式の代表と言えます.ACカップリングや光での高速・長距離伝送に最適な方式です.「クロックが埋め込まれている」と説明される場合がありますが,実際には特定の定期的な同期パターン(「K28.5コンマ・キャラクタ」と呼ばれる制御コード)で周波数やバウンダリ(境界)の情報を認識しています.

受信側でデータ'0'の数と'1'の数の差からデータ・エラーを判定可能なランニング・ディスパリティ機能を備えています.また,ランレングス('0','1'の連続数)が5以下などの特徴もあり,信頼性の高いコーディング方式といえます.

3) クロック埋め込み式(クロック・エンベデッド)SerDes

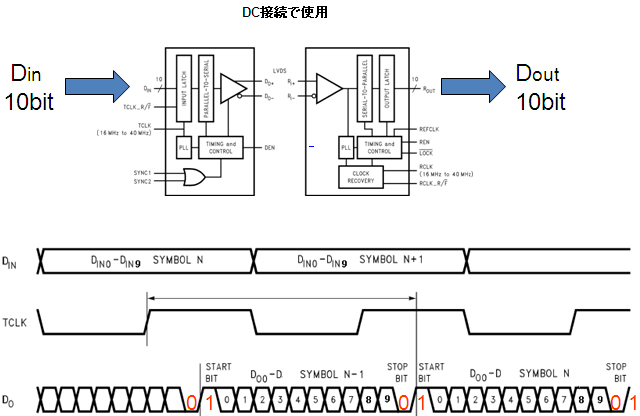

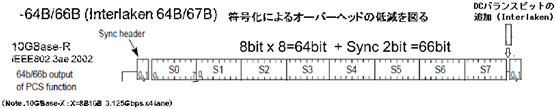

クロック埋め込み式SerDesは,シリアル・データの前と後ろにHigh,Lowのクロック情報を埋め込んでシリアル伝送する方式です.10B12B,64B66B,64B67B,128B130Bと呼ばれるコーディング方式も,このクロック埋め込み式です.別名,スタート・ストップ方式とも呼びます(図17,図18).

図17 10B12B SerDes

図18 10ギガビットEthernet(10GBASE-R)仕様の64B66Bコーディング

クロック・ビットとデータを区別できるように,データ・ビットは必ず'0'と'1'に変化することが条件です.これは,DCバランス・ビットによる全データ反転や,データ・スクランブルで実現しています.

データの前と後ろにクロックの'0','1'情報が必ず存在するので,この部分でデータのバウンダリを認識したり,PLL(Phase Locked Loop)の同期タイミングを取ったりしています.

内部回路については,LVDS SerDes回路の一部の機能を変更することで実現可能でした.LVDS SerDesのLVDSクロックとLVDSデータを1本のシリアル・ラインに埋め込むことで,ACタイミングの問題を物理的に解決し,長距離・高速伝送が可能になりました.

後に,DCバランス・ビットを追加し,ACカップリングをサポートした規格やデバイスも,現在では一般的になっています.DCバランス・ビットとは,送信側でシリアル・データ・ストリームの'0'の数と'1'の数の差を常に計算し,'0'の数と'1'の数の差が少なくなるように,このビットで送信シリアル・データの極性を決定する方法です.データが反転した場合でも,DCバランス・ビットの極性を確認することで,受信側はデータを正しく再生します.