ギガビット高速信号伝送を理解するための基礎知識(後編) ―― 特性インピーダンスからコーディング方式,SerDes回路,イコライザ補償まで

●終端方法の基本は同じ

数Gbpsの高速信号伝送を採用している規格が多くありますが,どの規格でも終端方法はシグナル・インテグリティ(信号品質)の要と言えます.物理層が異なると終端方法にも多少の違いがあり,さまざまな方法が利用されています.しかし,「終端抵抗により伝送路の特性インピーダンスとのマッチングをとる」という意味では,基本的にどの方法も同じです.伝送路の特性インピーダンスに合わせた終端抵抗を信号終端部分に配置し,片方を低インピーダンス・パスに接続する,という構成であればよく,ドライバ・レシーバ回路が動作しやすい電圧範囲に終端することも可能です.

以下に,代表的な終端方法と特徴を挙げます.

1) 受信端のGND/Vcc終端

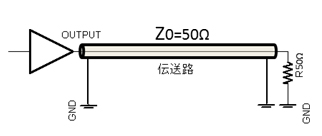

GNDやVccに対して終端抵抗を接続する方法があります.シングルエンド・ラインの特性インピーダンスに合わせて50Ω終端が多用されています.50Ωの終端を使用する場合,接続される伝送路の特性インピーダンスもシングルエンド50Ωを想定しています.50Ωで終端すると,例えば8mAの電流源でドライブしたとき,振幅はわずか400mVになります.

各種の高速信号伝送の規格で採用されているCML(Current Mode Logic)の受信端では,図6のようにVccにそれぞれ50Ω程度で終端されています.

図6 CMLディファレンシャル入力部(50Ω,Vcc終端)

また,測定器のBNC,N型,SMAなど,シングルエンド信号のコネクタの多くは50Ω終端です(図7).

図7 BNC,SMAコネクタ部(50Ω終端)

2) 受信端の差動ペア終端

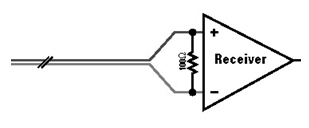

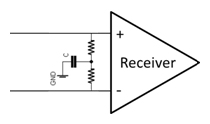

LVDSの差動ペアでは,信号の受信端部分で差動伝送路の特性インピーダンスに合わせ100Ω程度の抵抗で終端します(図8).

図8 差動ペア(受信端終端)

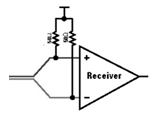

このLVDSの受信端ではコモン・モードが浮いている状態のため,二つの50Ω抵抗の間のコモン・モードに低インピーダンス・パスを設け,不要輻射ノイズを低減する方法も用いられます(図9).

図9 LVDS終端(コモン・モード・ノイズ低減回路付き)

3) 送信端の直列抵抗によるインピーダンス・マッチング

CMOSやTTLなどのシングルエンド信号を用いた基板上でのデバイス同士の接続やバス接続の伝送路では,受信端における終端は一般的ではありません.特性インピーダンスに合わせた終端抵抗がない伝送路では,受信端でインピーダンス・ミスマッチによる反射のエネルギーが送信端へ戻ってきます.このとき,50Ω伝送路ではドライバの出力インピーダンスを20~30Ω程度とすると,20~30Ω程度の直列抵抗を出力端子の直近に付けることで,受信端で反射し伝送路に戻ってきたエネルギーを送信端で吸収することができます.

送信端の直列抵抗による終端方法は,ある程度高速なシングルエンド信号の反射によるリンギングへの対策としてよく使用されています.リファレンス回路などでよく見かける構成です(本記事の前編の図16,図17を参照).

4) 両終端

送信側,受信側ともに伝送路の特性インピーダンスに合った終端を持つ構成も使われます.

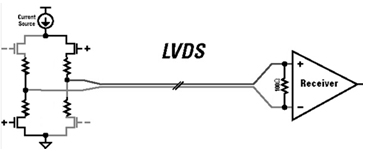

先ほどはLVDSレシーバの差動受信端終端を例に挙げました.一方,LVDSのドライバは,図10のような構成では送信端でインピーダンスのマッチングを取っています.差動100Ω程度(片方50Ω)になるように出力インピーダンスが作られたドライバは,低インピーダンス出力のバッファと比べるとエッジ・レートが遅くなりますが,送信端でも伝送路とのインピーダンスがマッチングしており,また受信端は100Ωなどの抵抗で終端されるため,反射のないきれいな信号伝送が可能となっています.

図10 LVDSドライバ・レシーバの構成

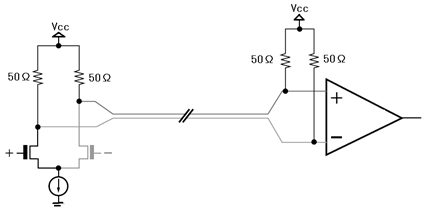

CMLでは図11のように送信・受信の双方とも50Ω程度で終端しています.等価回路をみると分かるように,ドライバの消費電力は大きくなります.

図11 CMLドライバ・レシーバの構成図

5) テブナン終端(1/2 Vcc終端を含む)

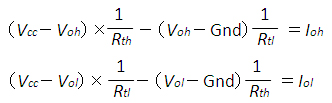

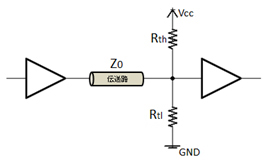

DDR(Double Data Rate)メモリ・インターフェースなどで使用される1/2 Vccにオフセットした終端や,PECL(Positive Emitter Coupled Logic)のVcc-2V終端は,テブナン終端の例です.図12のように,Vcc側とGND側の二つの抵抗を使用して特定のオフセット電圧を作ることができるため,受信端のレシーバの特性に合わせて自由に終端電圧を設定できます.

図12 テブナン終端

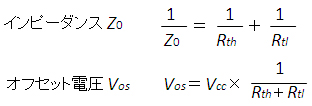

また,この二つの抵抗によるインピーダンスは,並列抵抗の式と同じように以下の簡単な計算で求めることができます.

例えばオフセット電圧1/2 Vcc,50Ωの伝送路では,この式からRthとRtlは100Ωとなります.また,信号のHigh,Low時にこの終端に流れる電流IohおよびIolは,以下の式で求められます.