インテグリティな技術コラム(8) ―― メモリ・バスの周波数特性と転送速度

●高速転送のために負荷の数を減らす

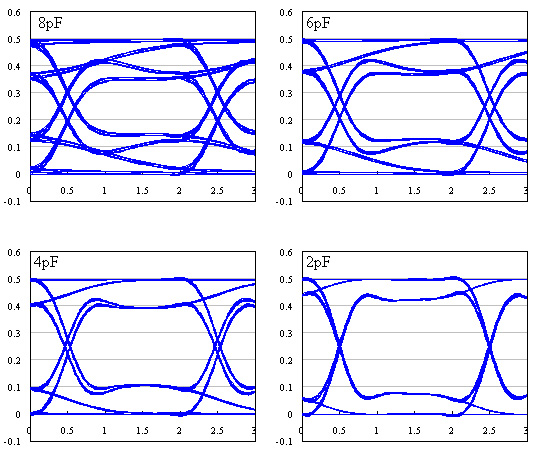

転送速度を上げるためにはバスの周波数帯域を広げればよい,ということが分かりました.メモリの端子容量が負荷となって帯域を下げているので,まずは端子容量を減らすことが第一の対応です.メモリ素子のプロセスの微細化により,端子容量は確実に減少してきました.図7は転送速度を500Mbpsに固定し,端子容量を変化させたときのアイ・パターンの変化を示しています.

図7 端子容量とアイ・パターン

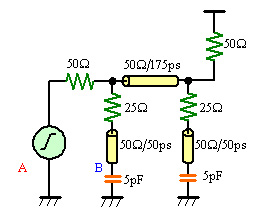

端子容量の減少により,アイ開口が広くなることが分かります.ただそれだけでは,高速化の要求に対応できません.最も効果的なのは,負荷の数を減らすことです.図8のように,負荷を半分の2個にしました.

図8 負荷が2個のSSTL回路

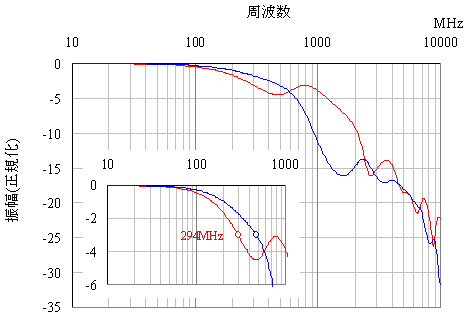

図9はそのときの周波数特性で,帯域は138MHzから294MHzと倍以上に広がりました.

図9 負荷が2個のときの周波数特性

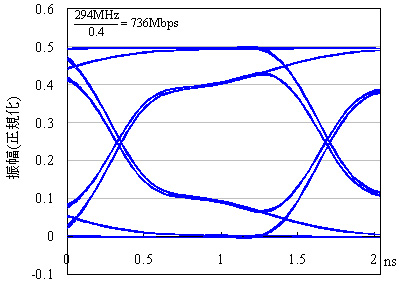

図10はこのときのアイ・パターンです.

図10 負荷が2個のときにアイ・パターン

ただし,負荷を減らすと搭載可能なメモリの数が減少するので,図8の回路を2チャネル用いて,いわゆるデュアルチャネル化しました.DDR3では,これをさらに3チャネルに増やし,帯域幅を単純計算で6倍に増加させました.

●行く着く先は,ポイント・ツー・ポイントの1対1伝送

4個の負荷の1チャネルから2個の負荷の2チャネルになって転送速度は向上し,多チャネル化によるバンド幅の向上が達成できました.この傾向が続くなら,「次は1個の負荷で4チャネル」になることは,専門家でなくても想像がつきます.負荷が1個はもはやバスではなく,ポイント・ツー・ポイントの1対1伝送です.

DDR3の後継のDDR4について,正式にはアナウンスされていませんが,噂によるとこのようになりそうです.メモリ・モジュールの増設はどうするのか,そんなに帯域幅を必要としない装置ではどうなるのか,少しややこしくなりそうです.

うすい・ゆうぞう

シグナル インテグリティ コンサルタント

http://home.wondernet.ne.jp/~usuiy/

Post a Comment