民生機器向けSOC開発と先端的セキュリティ処理のIPコア化 ―― CyberWorkBenchの活用事例

tag: 半導体 ディジタル・デザイン

技術解説 2009年7月 2日

● 動作合成を利用して迅速に性能見積もり

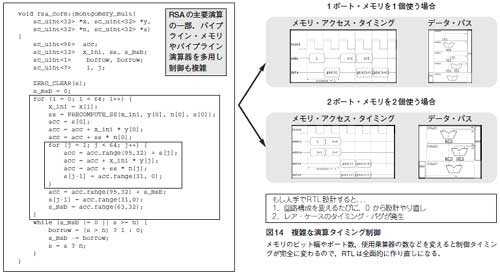

ここでCWBの動作合成が大いに役立ちました.楕円暗号ユニットやモジュロ(RSA)演算ユニットの内部構成をさまざまに変えて性能を綿密に調べるのは,人手によるRTL設計ではとても不可能だからです注8.これらは演算タイミング制御が複雑で,RTL設計が際立って難しい回路です(7).また,図12の通り多くの最適化項目があります.メモリのビット幅やポート数,使用乗算器の数などを変えると制御タイミングが完全に変わるので,RTL全面的に作り直しになってしまいます(図14).

図14 複雑な演算タイミング制御

メモリのビット幅やポート数,使用乗算器の数などを変えると制御タイミングが完全に変わるので,RTLは全面的に作り直しになる.(クリックすると拡大します)

CWBを使い,表1のように多くの性能評価データを短期に蓄積しました.メモリ・タイプなどをディレクティブで切り替えることができ,人手によるRTL設計に近い品質の回路が得られるので(表2),信頼性の高い性能見積もりができました.なお,パイプライン・メモリへのアクセスが性能上クリティカルなのですが,これを連続的に行うようきちんと最適化されることが,人手によるRTL設計と同等の性能を得られる理由の一つです.

表1 性能評価データ(楕円乗算の例)

表2 動作合成と人手による設計の性能比較(RSAの例)

注8: 大まかには気丈の理論検討で予想できるが,正確なところは作ってみないとなかなか分からない(特に回路規模).論理検討だけでは見落としも生じる.

● 性能見積もりデータをもとにアーキテクチャ決定

こうして得られた各ユニットの性能評価結果をもとに,アーキテクチャを決定しました(図13).ユニット内の演算時間が大半で通信時間はわずかであることが分かったため,全ユニットを1本のバスで結合した単純な構成にしてあります注9.全体動作制御部(データ転送コントローラ)もこのバスにつながります.ユニットの個数を増やして並列化した場合の全体性能も調べ,回路規模とバランスが取れている点を選びました(詳しくは文献(5)を参照).

注9: 公開鍵系のアプリケーションに特有な結果といえる.画像処理や共通鍵系では,大量のストリーム・データを扱うことと,ユニット内部処理よりも通信の方が速度上のネックであることから,ユニットを直接統合するアーキテクチャになりやすい.その場合,全体制御の組み込みがやや難しくなる.

● ステップ4:全体のインテグレートと検証

続いて,各ユニットを動作合成してから基本アーキテクチャ通りに結合して,全体の機能検証や性能確認を行いました.機能検証の際に問題が出る可能性がある個所は,全体動作制御やユニット間通信です.

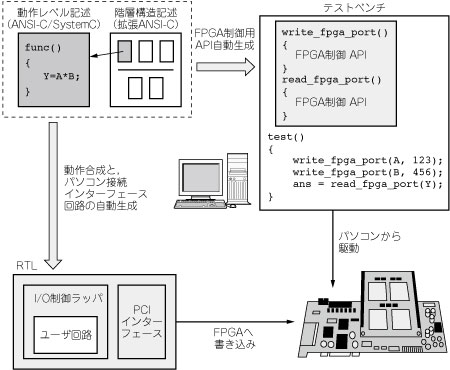

今回は,全回路をFPGA上に実装して全体検証を行いました.FPGAは信号の観測性が低く,動作の細かいデバッグには向きませんが,今回はユニット接続用バス(APB相当)をCWBに自動生成させたことや,全体制御シーケンスが難しくないこと,各ユニットで動作合成出力のRTLをそのまま用いたことなどから,最初からまとめてFPGAへ持っていっても問題ないと判断しました(図15).実際,機能面のバグは何も出ませんでしたし,予想通りの性能が得られました.検証というよりも,確認といったところです.

図15 FPGAによる全体動作の検証

ユニット接続用バスをCWBに自動生成させたことや,全体制御シーケンスが難しくないこと,各ユニットで動作合成出力のRTLをそのまま用いたことなどから,最初からまとめてFPGAへ持っていっても問題ないと判断した.

一般的には,全体検証をトランザクション・レベルや動作レベルで行う方がよいでしょう.ただし,既存のRTLのIPコアや実機デバイス(メカやチップ)との統合動作,マルチクロックや可変速度クロックによる動作など,FPGA上でないと適切なチェックができない事項も多々あります.また,仮にC言語上で機能検証をしてあったとしても,FPGAまたはRTLシミュレータでロングランを実施するべきです注10.

なお,動作合成が生成するRTLでタイミング・クロージャに失敗するようなことはほとんどなく,今回も基本アーキテクチャ確定後の作業の手戻りはありませんでした.今回は問題になりませんでしたが,場合によってセルフテスト(BIST)機能の追加や設計階層の調整が必要になるのは,RTL設計の場合と同じです.

注10: C-RTL等価性照明は,RTL-ゲート等価性証明ほどにはこなれいてない.回路機能や規模に対する制限もあり,今回のような回路を一気に扱えるほどではない.

● 無事に目標性能を達成できた

以上の過程を経てグループ署名IPコアを完成させることができました.このIPコアは100M~200MHzクロック時に0.05~0.1sで署名生成・検証を行うことができます.同一クロックのパソコン用ソフトウェアと比べれば30~40倍の速度です(回路規模は約300万ゲート).組み込み機器中でも最新のパソコンと同等の速度が得られることになり,回路化の目的を達することができました.

● 高度処理を回路化するうえで動作合成は必要不可欠

本開発事例の最大の成功要因は,Cベース設計でセキュリティ専門家の積極的な参加が可能になったことです.処理が難解なうえに,ソフトウェア用とハードウェア用でアルゴリズムに大きなギャップがあり,回路設計サイド単独で作りきることは不可能でした.高度処理の実装にはドメイン知識が必要不可欠であることから,今後,専門家とのコラボレーションの必要性はますます高まっていくでしょう.

動作合成については,「ソフトウェアから回路を作成できる」,「ハードウェア構造をまったく意識しなくても回路を作成できる」などといわれることもありますが,本事例の通り,実際はそこまで単純ではありません(論理合成が出たときと同じ).合成技術が進歩すれば,設計対象の複雑さや要求性能もまた上がっていくので,どうしてもハードウェアの全体構造や大局的並列性を意識せざるを得なくなるからです.とはいっても,動作合成で設計抽象度を上げないことには,やはり高度処理の回路化ができません.そのような実事例が既に幾つも出てきています.

* * *

本稿の一部は,総務省の委託研究「情報の来歴管理等の高度化・容易化に関する研究開発」プロジェクトの成果です.

参考・引用*文献

(1 )CyberWorkBenchのホームページ, http://www.necst.co.jp/product/cwb/ja/

(2 )特集1 動的再構成可能デバイス,その素性と実力,Design Wave Magazine,2004年8月号,pp.20-78.

(3 )本村真人;Cベース プログラマブルHWコア「STPエンジン」の現状と展望,信学技報,Vol.108,No.300,RECONF2008-48,pp.51-56,2008年11月(デザインガイア 招待講演).

(4 )NECエレクトロニクスの動的再構成デバイス,

http://www.necel.com/programmable/

(5 )特集2 LSIを盗聴から守る,Design Wave Magazine,2006年2月号,pp.100-134.

(6 )Sumio Morioka, Toshinori Araki, Toshiyuki Issihiki, Satoshi Obana, Kazue Sako and Isamu Teranishi;Architecture Opti

mization of a Group Signature Circuit,情処研報,Vol.2008,No.71,CSEC-42, pp.171-178,2008年7月(グループ署名回路のアーキテクチャ).

(7 )森岡澄夫;特集1 アルゴリズムのハードウェア化手法,Design Wave Magazine,2008年1月号,pp.20-70.

(8 )ET2008レポート,組み込みネット.

http://www.kumikomi.net/article/report/2008/55et/01.html

もりおか・すみお

森岡澄夫.NTT,IBM,ソニーの各社で,誤り訂正・暗号・画像処理の高性能IPコア,SOC研究開発に従事.ゲーム機搭載セキュリティ・システム回路の開発でSony MVP受賞.現在はNEC中央研究所にて,動作合成を活用したIPコアの研究開発を行っている.博士(工学),CRYPTREC暗号モジュール委員会委員,ASP-DAC 2009 OCメンバ.

s-morioka@ak.jp.nec.com