民生機器向けSOC開発と先端的セキュリティ処理のIPコア化 ―― CyberWorkBenchの活用事例

tag: 半導体 ディジタル・デザイン

技術解説 2009年7月 2日

● 障壁1:仕様理解や回路へのブレークダウンができない

最近のアルゴリズム処理では,数学的に高度な演算がなされることが珍しくなくなっています.グループ署名も多分に漏れず,楕円曲線上の有限体演算や整数上のべき乗剰余演算などが複雑に絡み合ったものです(5)(図7).学会でも先端的な話なので,暗号の教科書を眺める程度では,とても実用品を作れる水準の知識を得られません.

このため,従来のIPコアと同様に開発作業を進めることはとても無理でした.すなわち,

- 抽象的な数式で書かれた仕様を理解

- 回路実装可能になるまで計算方法をブレークダウン

- 回路に向いた処理方式に修正

- 性能を達成できる回路構成を考える

- RTLコードで実装する

- テスト環境を構築して検証

という一連の作業を,回路設計サイドではもう行いきれなくなったのです注5(図8).また,グループ署名処理の専門家ではないため,本来やってはならない改変や間違いに気付かないリスクも,無視できなくなりました.

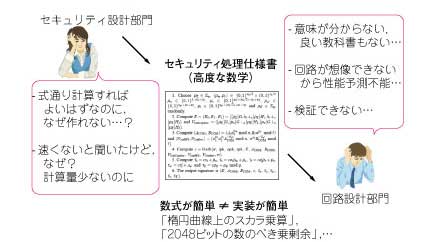

図8 仕様理解や回路へのブレークダウンができない

学会でも先端的な話なので,暗号の教科書を眺める程度では,とても実用品を作れる水準の知識を得られない.このため,従来のIPコアと同様に開発作業を進めることは無理.

一方,セキュリティ側では,回路実装にあたって一体何が問題なのかが分からない状況でした.このままでは話が進みません.

注5:筆者はセキュリティ・システム回路の設計に長らく関わってきており,ある程度の予備知識や経験はあったが,それでも容易とは言い難い状況だった.

● 障壁2:要求性能の達成方法が分からない

回路を設計する際には,技術面だけ実現できればよいのではなく,達成すべき性能値が必ずついてまわります.今回も利便性を確保できる処理速度(例えば200MHz動作時に0.1秒)が達成できなかったり,組み込みプロセッサよりも遅くなったりしては,回路化する意味がありません.速度だけでなく,回路規模が1億ゲートになったり必要メモリが100Mバイトになったりしてもいけません.

従って,本格的な実装に入る前に性能達成の見通しを立てる必要がありますが,それをどのような方法で行うべきかが問題となりました.

● 障壁3:新規アルゴリズムなのでテスト・データがない

従来のIPコア開発でも必ず問題になってきた事項ですが,いっそう顕著になりました.処理内容が難しいうえ,これまでになかった新しい処理であるため,回路設計サイドでテスト・データを準備することは不可能でした.

● 障壁4:デバッグやロングラン・テストができない

既存の公開鍵暗号では,作った回路の検証がとても大変でした.RTLシミュレーションに非常に時間がかかったからです.例えば図9の通り,2048ビットRSA暗号化のRTLシミュレーションに,最新のパソコンでも10分近い時間がかかります注6(復号化ははるかに長い時間がかかる).

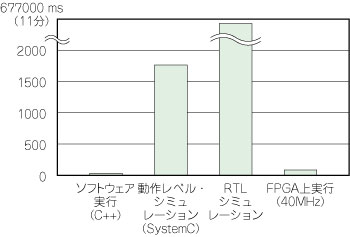

図9 シミュレーション時間の例

2048ビットRSA暗号化の検証時間の例を示す.RTLシミュレーションは最新のパソコンでも10分近い時間がかかる.もしグループ署名処理全体をRTLシミュレーションしたら,1日かけても終わらない.

グループ署名の場合,公開鍵暗号で使われている演算が多数組み合わさっているため(図7),単純計算でも1回のRTLシミュレーションに日単位の時間がかかると予想されました.これではデバッグもロングラン・テストも不可能です.

注6:動作レベル・シミュレーションについては,本稿でも述べる通り,処理アルゴリズムなどをハードウェア向けに修正した後のコードなので,純粋なソフトウェア用コードよりかなり遅くなる.FPGAについては,処理自体の実行速度より,パソコン⇔FPGA間のデータ転送速度の方がネックになりやすいので要注意.