民生機器向けSOC開発と先端的セキュリティ処理のIPコア化 ―― CyberWorkBenchの活用事例

tag: 半導体 ディジタル・デザイン

技術解説 2009年7月 2日

2. すっかり定着した製品設計での利用

● 古くからの利用実績があり導入リスクが低い

CWBの特徴の一つは,製品用LSI設計に長年使われてきていることです.一般にこのような高位合成ツールは,厳しい実設計の世界で十分にもむ必要があります注1.

LSI設計では,すべてのバグをチップ製造前に発見・排斥するために,膨大な手間を検証に費やしています.それなのにツールが合成を間違えてレアケース・バグを勝手に仕込んだりしては,話になりません.一見華々しい機能があったとしても,信用のできないツールでは恐ろしくて使えません.

CWBは,1993年に最初の製品用LSI開発への適用が行われ,それ以来多数の実設計でもまれてきています(1).NECのみならず,複数の大手メーカでも製品開発に利用されています.実製品の開発実績は豊富です.

注1:事情はソフトウェアのコンパイラと似ている.高度な最適化をするコンパイラほど,さまざまなバグが入りがちである.利用者が少なく枯れていないコンパイラはバグだらけで,生成されたアセンブラを見てバグ回避しつつ使うはめになったりする.しかし,そのような品質水準のツールを,製品LSIの開発に使用するわけにはいかない.

● 携帯電話搭載SOCへの適用

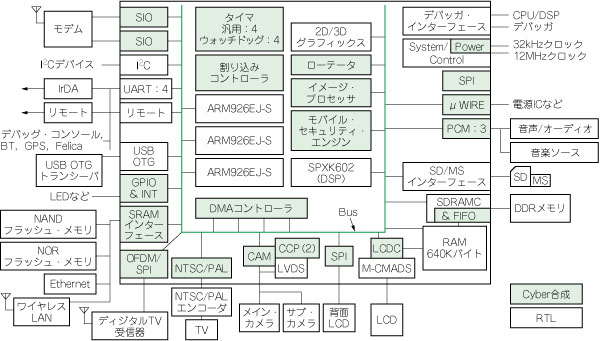

実製品への適用の代表的事例として,最近の携帯電話用SOCを紹介します.CWB動作合成の適用状況を図3に示します.

図3 携帯電話向けSOCにおける適用

着色部がCWBによって作成されたコンポーネント・アルゴリズム処理だけでなくインターフェースにも適用.

見ての通り,多くのコンポーネントがCWBによって作られています.注目していただきたいのは,DMAコントローラや各種I/Oインターフェース回路にも多用されていることです.このようなアルゴリズム主体ではない回路であっても,単なる信号ON/OFFに留まらず,コマンドやデータの解釈,条件判断,パリティ計算など,込み入った処理が必要になってくる場合が多々あります(最近はプロトコルなどが複雑化し,そうした傾向が強まっている).そのような個所ではHDLよりC言語を使うほうが設計しやすいのが,CWBが使われる理由の一つです.

もちろん,画像加工やセキュリティなどアルゴリズム主体の処理は,動作合成が最も得意とする分野でもあり,CWBで回路化されています.

CWBが使われていない個所もあります.その大半は,既存の設計資産をそのまま流用したり,プロセッサや市販IPコアを購入してはめ込んだりした部分です.

図3の事例より後の開発でも,スクラッチ設計するコンポーネントではCベース設計が主に利用されています.

3. 動的再構成デバイスの開発環境としての利用

ここからはCベース設計によって初めて可能になる回路設計スタイルを紹介します.最初に,動的再構成デバイスを取り上げます.

● 実用化が着実に進んでいる動的再構成デバイス

動的再構成デバイス(Dynamically Reconfigurable Device)は,動作中に論理構成を切り替えることができるプログラマブル・デバイスです.プログラマブルという点はFPGAやCPLDと同じですが,切り替えが非常に高速に行えることや(デバイスにもよるが数クロック),動作時の状況に応じて回路構成を変えられること,SOC上にIPコアとして搭載可能であることなどが異なります.

動的再構成デバイスが研究レベルで登場したのは1990年代後半で,さすがに登場当時のブームは終わっています.しかし実用化が着実に進展して,製品への搭載も広まりつつあることから,昨今では第2次ブームともいえる状況になってきています(8).

このデバイスが特に役立つのは,組み込みプロセッサでは処理能力がまったく足りず,プログラマビリティが欲しいがFPGAチップの搭載はできない注2,という場合です.例えば民生機器で使われるCODEC処理や通信処理などでは,仕様(規格)が未定のまま回路設計を始めなければならなかったり,製品化後に新規格が出たり,という事態がしばしば起きます.そこで動的再構成デバイスをSOCに搭載しておくことによって,機器の短期開発,SOC開発失敗リスクの回避,機器出荷後のアップグレードなどが可能になります.実際に,さまざまな民生品でそれが実証されてきています.

注2:価格や消費電力,小型化,設計情報保護などの観点から.

● Cベース設計によりデバイスのメリットを引き出せる

動的再構成デバイスに限らず,プロセッサやFPGAなどあらゆるハードウェア・プラットフォームにおいて最大の問題となるのが,アプリケーションの開発環境です.いくらハードウェアの潜在的能力が高くても,それを容易に引き出せる開発環境がないと宝の持ち腐れになってしまいます.

動的再構成デバイスについても,もし設計エントリがRTLだったらどうなるでしょうか.せっかく開発期間の短縮や処理変更の容易さを狙っているのに,回路設計が難しくては効果を望めません.開発環境があまりに貧弱だと,普通のスタンダード・セルASICと比べても,はるかに設計が難しくなってしまうかもしれません.

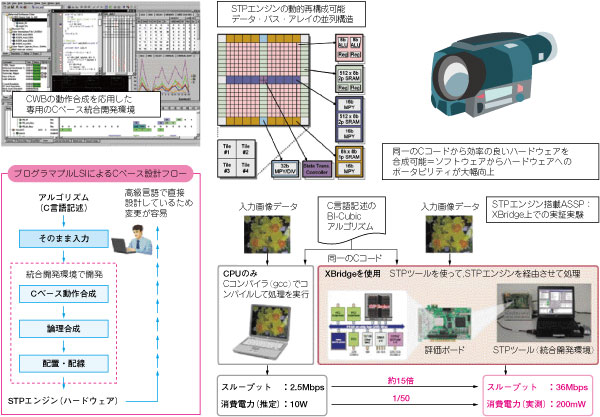

CWBは,NECエレクトロニクスの動的再構成デバイス(2),(3),(4)のアプリケーション開発環境にも応用されています(図4).C言語でアルゴリズムを書きさえすれば,基本的に自動でデバイスへのマッピングがなされ,ICE(In-circuit Emulator)のような実機デバッグも可能です.デバイスの能力を限界まで使い切る場合を除き,設計者はデバイス内部の構造を綿密に把握・意識する必要はありません.

図4 動的再構成デバイスの開発環境と特徴