応用回路設計のための第一歩 ―― I/O規格とLED表示,スイッチ入力,アナログ出力,RS-232通信のための回路の設計法

tag: 半導体 電子回路 ディジタル・デザイン

技術解説 2009年5月18日

ここでは,FPGAのI/O端子に外部デバイスを接続する方法を説明します.I/O規格について説明した後,LEDやスイッチ,はしご型(ラダー)DACを使ったアナログ出力,RS-232通信のためのトランシーバ/レシーバICとのインターフェースについて説明します.(編集部)

付属FPGA基板では,I/O電圧が3.3Vに設定されています.ここでは,LEDやスイッチなどをFPGAから制御するときに使用されるI/Oピンに関して,I/O電圧が3.3Vの場合の使い方や注意点について説明します.

1.FPGAのI/O電圧とI/O規格

● 付属FPGA基板のI/O電圧は3.3V

物理的な素子と素子を接続することを「インターフェースする」といいます.米国Lattice Semiconductor社のLatticeXP2のようなFPGAのI/Oピンに,LEDやスイッチ,ほかのディジタルLSI(マイコンなど)を接続する場合には,I/Oピンのインターフェースを理解する必要があります.

付属FPGA基板は,I/O電圧が3.3Vに設定されています.この電圧は変更できません.この場合,I/Oインターフェースは最大で3.3Vとなるような信号レベルの回路設計を行う必要があります.一般的にLVTTLかLVCMOSが使用されます.

● LVTTLとLVCMOSを使用する

LVTTLやLVCMOSは,入出力する信号の電圧レベルで,どのような電圧まで保証されているかということが規定されたI/O規格です(表1).

表1 I/O規格で規定されている電圧の例

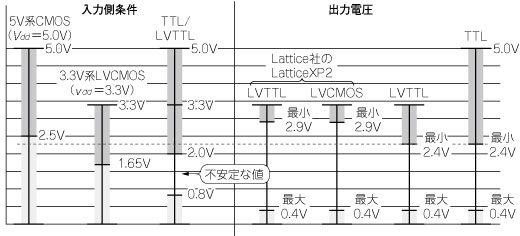

例えばLVTTLとLVCMOSとでは,信号入力時の規定に大きな違いがあります(図1).3.3VのLVTTLは,入力電圧が2.0V以上のときにHレベル,0.8V以下のときにLレベルと判断します.これに対して,LVCMOSは,1.65V(Vcc×50%)より上のときHレベル,下のときLレベルと判断します.

図1 LVTTLとLVCMOSの入出力電圧レベルの比較

例えば,外部からケーブルを伝わってきた信号が1.5Vだったとします.LVCMOSの入力ピンでは「Lレベルである」と認識されます.しかしLVTTLでは,HレベルでもLレベルでもない,「不安定な値」になってしまいます.

LVCMOSの出力信号は,Vccの90%と10%を保証できるような電圧が出力されます.LVTTLの出力信号は,LVCMOSほどしっかりと電源電圧の範囲まで振られないのが普通です.

● 異なるI/O規格のICをつなぐと不具合が...

出力側と入力側のI/O規格が異なると,不具合を招く可能性があります.LVCMOSの出力信号ならLVTTLの入力ピンに接続できますが,LVTTLの出力信号をCMOSの入力ピンに接続すると,正しく信号が伝送できないことがあります.ここでは注意が必要ないくつかの例を紹介します.

(1)5V系のデバイスを駆動できない

一昔前の製品は,5.0Vの電源電圧で駆動する半導体が多用されていました.このため,今でも5.0VのI/O規格を利用する機器が数多くあります.

5.0VのCMOSの場合,入力側は2.5Vをしきい値としてHレベルとLレベルを判断します.ここにVOHが2.4V以上のLVTTL信号を接続した場合,わずか0.1Vではありますが,信号の伝達が保証できません.逆にLVCMOSであればVOHが2.96V以上ですから,5VのTTLインターフェースに対しても正しく信号伝送が行えます.

(2)5V系の信号はFPGAの破壊を招く恐れがある

5V TTLの信号を3.3VインターフェースのFPGAなどに接続する場合を考えます.

TTLではVOHが最小2.4Vと規定されていますから,一見,インターフェースできそうです.しかしTTLの場合,Hレベル時の出力電圧は最大で5.0V近くになる可能性があります.つまり,FPGAには5.0Vが印加される可能性があるということです.

LatticeXP2の場合,3.3VのLVTTL/LVCMOSインターフェースに設定した場合は,最大入力電圧は3.6VとDC特性で規定されています.また,絶対最大定格は3.75Vです.つまり,5.0V系の信号を入力すると,FPGAが破壊されてしまう可能性があります.そのため,5.0V系の信号を直接FPGAに入れることはできません.本来であれば3.3Vを超えないように注意しなければなりません.

● 電圧レベルの異なる規格間のインターフェース法

電圧レベルの異なるインターフェース間で信号伝達を行う必要は,さまざまな場面であります.このような場合,レベル変換機能が内蔵されているバス・バッファICを用いるか,オープン・ドレインICを使うことでインターフェース可能になります.

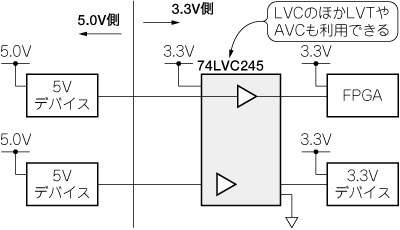

(1)バス・バッファの利用

バス・バッファICは,信号の駆動能力を向上させるバッファという本来の機能以外に,高い入力電圧に耐えられる構造になっています.具体的には3.3Vで動作させていても5.0V入力を許容しているICが数多くあります.

そこで図2にような回路を用いることで,5V系の出力信号を3.3V系のデバイスに接続できます.

図2 バス・バッファICによる5V→3.3Vインターフェース方式

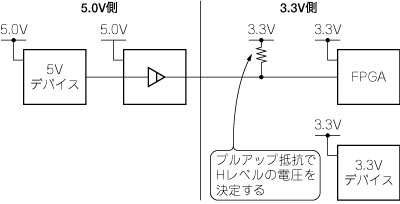

(2)オープン・ドレインICの利用

オープン・ドレインICは,バス・バッファICの簡易版と考えて差し支えありません.違いはIC内部の出力回路部分を簡略化することで,Lレベルの出力はできるが,Hレベルの出力に関しては電圧を出力しないというものです.Hレベルを出力しないと,何の役に立つのかと疑問に思うかもしれません.これは出力電圧を得る方法はユーザに委ねられていることを意味します.

オープン・ドレインICでは出力電圧を得るために,外部にHレベルにしたい電源電圧と抵抗素子を接続します.これにより,Hレベルは1Vだろうが2.5Vだろうが,48Vだろうが,ICが破壊されない限り任意の電源電圧に決められるわけです.オープン・ドレインICの出力端子に,3.3Vに直結した抵抗素子を用意すれば,Hレベルは3.3Vになります(図3).

図3 オープン・ドレインICによる5V→3.3Vインターフェース方式

オープン・ドレインICは,一般的にバス・バッファICよりも低コストです.外部抵抗素子が必要になることと,抵抗を介してHレベルに電圧を引き上げるために時間がかかる,すなわち最大動作周波数が低くなりがちであるという点に注意が必要です.

(3)抵抗で分圧する

このほか5V系の信号の出力電圧が確実な場合,例えば0Vと5Vであるというように保証されているなら,もっと単純に2個の抵抗を使って分圧する方法もあります.

例えば,2個の100Ω抵抗があれば,1/2の電圧を作れます.これで5V→2.5Vのレベル変換ができます.これならLVTTLでもLVCMOSでも,どの3.3Vインターフェースでも接続が可能です.

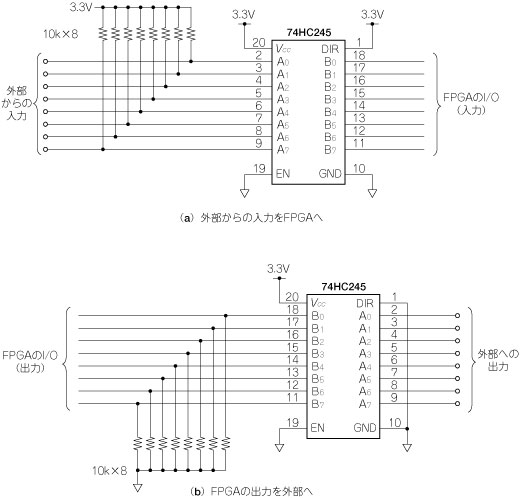

● FPGAの保護にバス・バッファを利用

FPGAの評価や実験で使う基板の場合,I/Oピンにどのような周辺デバイスが接続されるか分かりません.このようなときに,電圧レベル変換やバス・バッファICなどを使用することで,FPGAを保護しつつ正しく信号レベルを伝達できます.回路の例を図4に示します.

図4 バス・バッファICによる入出力保護回路