応用回路設計のための第一歩 ―― I/O規格とLED表示,スイッチ入力,アナログ出力,RS-232通信のための回路の設計法

tag: 半導体 電子回路 ディジタル・デザイン

技術解説 2009年5月18日

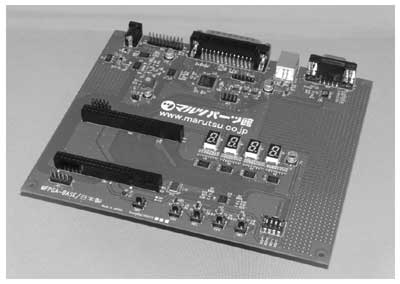

本稿で解説した各機能を搭載したFPGA周辺機能ボード(以下,ベース・ボードと呼ぶ)がマルツパーツ館から発売される予定です.I/Oにつながる回路のほか,FPGAを動作させるために必要な回路も含まれています(写真A).

写真A FPGA周辺機能ボードの外観

●FPGAを動作させるための回路

(1)FPGA基板実装部

ベース・ボードには,付属FPGA基板を搭載するコネクタが用意されています.ベース・ボードの各I/O機能は,このコネクタを介してFPGAから制御できます.また,ベース・ボード上に搭載されているJTAGダウンロード機能用の専用信号ピンも含まれています.過去にCQ出版社が雑誌に付属したFPGA基板とある程度の互換性があります.

(2)JTAGダウンロード・ボード部

ベース・ボードの特徴は,さまざまなメーカのFPGAに対応しているということです.本誌付属FPGA基板向けのLattice社のほか,Altera社とXilinx社のパラレル・ポートJTAGダウンロード回路と同等品が搭載されています.ターゲットFPGAのメーカは,ジャンパで設定します.

JTAGのダウンロードを行うためには,パソコン側にはDサブ25ピン形状のLPTポートが搭載されている必要があります.パソコンと本ボードを接続するために,Dサブ25ピンのストレート・ケーブルを用意する必要があります.

(3)電源供給部

5V~6Vの電源を3.3Vに変換して,FPGA基板やそのほかの回路に供給します.供給可能な電流は最大1.0Aを想定して設計されています.

(4)リセット回路

ベース・ボードには,リセット・スイッチが用意されています.このスイッチの押下によって駆動される信号は,システム・リセットの役目を持たせています.

- 電源投入直後のパワーONリセットを発光する(電圧監視)

- 3.3Vの電源電圧が低下することで,パワーONリセットを発行する(電圧監視)

- リセット信号を発行する(マニュアル・リセット)

(5)クロック・オシレータ部

一般的にFPGAで回路設計を行う場合には,なんらかのクロックを使用します.ベース・ボードでは,10MHzのクロックを発生させる水晶発振器(クロック・オシレータ)をあらかじめ搭載されています.

●I/O機能

(1)7セグメントLED部

ベース・ボードには4けた分の7セグメントLEDが搭載されています.スタティック点灯方式によって,点灯と消灯が可能です.つまり,複雑な操作を伴わずに,FPGAのI/OピンからHレベルまたはLレベルを出力することで,LEDを点灯/消灯できます.

FPGAからはLレベルの出力を行うと,対応する7セグメントLEDのエレメントは「点灯」します.

逆にHレベルの出力を行うと,今度は「消灯」します.

(2)スイッチ入力部

ベース・ボードには,4個のタクタイル・スイッチと4ビット分のDIPスイッチが搭載されています.

タクタイル・スイッチの回路には抵抗とコンデンサによるフィルタと,シュミット・トリガ・インバータICによるチャタリング除去回路が組み込まれています.

4ビット分のDIPスイッチは,プルアップ抵抗が実装されただけの簡単な機構です.頻繁にON/OFFすることは想定されていません.

(3)RS-232シリアル通信部

パソコンとの通信方法として,簡単に機能検査ができるシリアル通信機能があると,なにかと便利です.

ベース・ボードには2線式のシリアル通信機能があります.シリアル通信部分にはRS‐232ドライバICが搭載されているため,パソコンとはDサブ9ピン形状のストレート・ケーブルを介して接続することで,通信が可能です.

なお,転送レートはドライバICの機能制約上,最大転送レートが430Kbpsまでです.

(4)パラレルI/O部

ベース・ボードには8ビットの入力ポートと,8ビットの出力ポートが用意されています.

ポートのコネクタとFPGAの間にはバッファが挿入されています.これは過電圧が入力されたり,出力電流をFPGAは十分に流せないということで,過負荷をFPGAにかけないためです.

(5)8ビット分解能R-2Rはしご型DAC部

ベース・ボードには,8ビット分解能のD-Aコンバータが搭載されています.D-Aコンバータは,パラレルI/O部のうち,8ビット・ディジタル出力太共通の信号線を使用します.そこでDAC出力イネーブル信号を用意しています.

いくら・まさみ

来栖川電工(有)

FPGAコンソーシアム会員