次世代DRAM規格「DDR4」と新技術規格「3DS」の概要を公表 ―― Server Memory Forum 2011

●ECC付きSoDIMMを追加,2スロットを維持

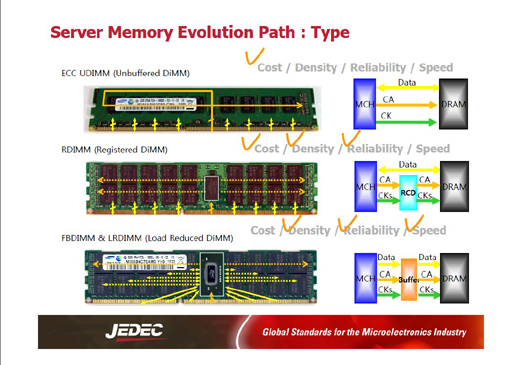

続いてメモリ・モジュールの概要を紹介しよう.現行世代のDDR3メモリ・モジュールでは,UDIMM(Unbuffered DIMM),RDIMM(Registered DIMM),LRDIMM(Load Reduced DIMM),SoDIMM(Small Outline DIMM)が規格化されてきた.DDR4のメモリ・モジュールには,DDR3で規格化されてきたこれらのDIMMに加えて,ECC(Error Checking and Correcting) SoDIMMが追加される予定である(図4).

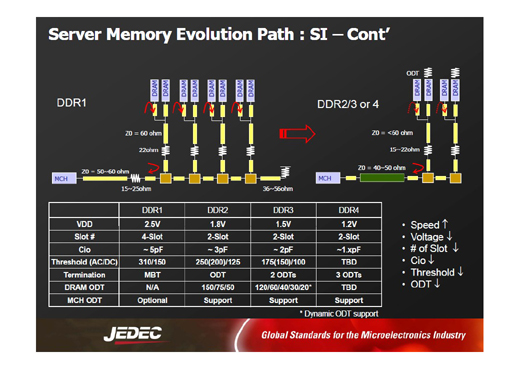

DRAMコントローラと接続されるDIMMスロットの数は,DDR3と同じ2スロットとなる.前世代のDDR2以降,3世代続けて2スロットが維持される(図5).

図5 DDR(DDR1)/DDR2/DDR3/DDR4モジュールのスロット数と配線インピーダンス

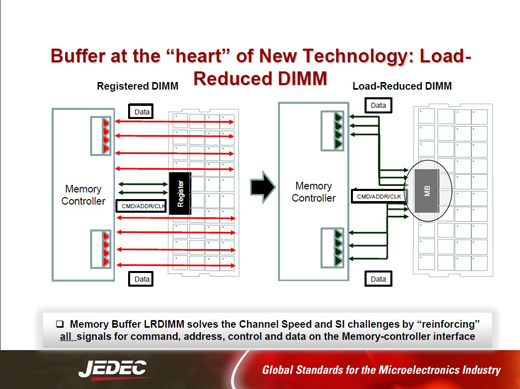

ここでUDIMMとは最も単純なモジュールで,SDRAMを基板に並べたモジュールである.DRAMコントローラとはスロット経由で直結される.RDIMMとは,レジスタICによってコマンド/アドレス(C/A)信号とクロック(CK)信号をコントローラとSDRAMの間でバッファリングしたモジュールであり,信頼性の向上やモジュール容量の拡大などが見込める.LRDIMMとは,バッファICによってC/A信号とCK信号に加えてデータ信号を含めたすべての信号をコントローラとSDRAMの間でバッファリングしたモジュールである.データ・バスの負荷容量を低減することで高速化と大容量化が狙える(図6).

図6 RDIMM(Registered DIMM)(左側)とLRDIMM(Load Reduced DIMM)(右側)の違い

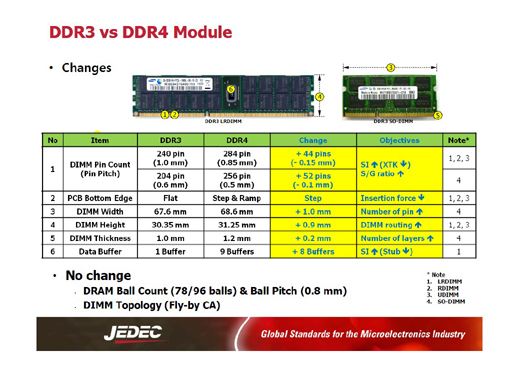

またDDR4モジュールはDDR3モジュールに比べると,ピン数の増加,ピン・ピッチの縮小,基板厚みの増加(配線層数の増加),バッファ数の増加といった変更がなされている.特に目立つのはピン数の増加で,DDR3の240/204ピン(204ピンはSoDIMM)から,DDR4では284/256ピンへと大幅に増える(図7).

●高速化の切り札となる「3DS」技術

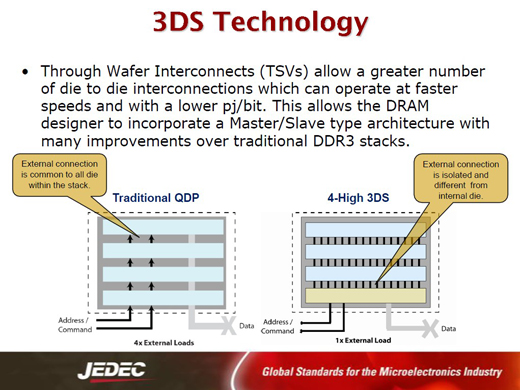

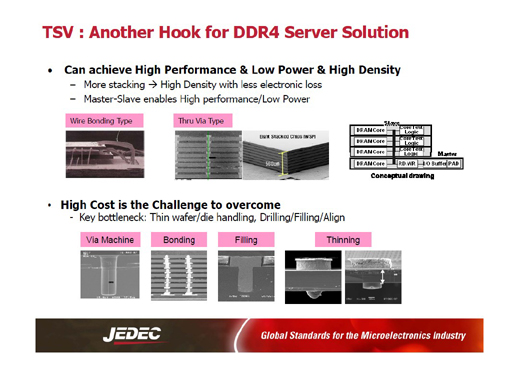

最後は,次世代マルチチップ・パッケージ規格「3DS」の概要を報告する.「3DS(Three Dimentional Stack)」とは,シリコン貫通電極(TSV:Through Silicon Via)技術によって複数枚のシリコン・ダイを積層する技術を応用した規格である.ここでTSV技術とは,積み重ねたシリコン・ダイを貫通する細長い柱状の金属電極で,上下のシリコン・ダイを電気的および機械的に接続する技術である.

従来,シリコン・ダイを積層するパッケージング技術には接着剤とワイヤ・ボンディングが使われてきた.積み重ねたシリコン・ダイを機械的に接続するのが接着剤であり,電気的に接続するのがワイヤ・ボンディングという役割分担になっている.TSVを採用したシリコン・ダイ接続技術には,従来技術に比べると接続配線長がきわめて短い,500点~1000点といった数多くの接続点を作れる,といった利点があり,高速性を重視する半導体チップに向く(図8).

図8 ワイヤ・ボンディングによるシリコン・ダイ積層(上左)とTSVによるシリコン・ダイ積層(上右)

「3DS」ではさらに,「マスタ・スレーブ」と呼ぶアーキテクチャを導入している.これは積層するシリコン・ダイの中で1枚だけがマスタとなり,パッケージの外部と信号をやり取りする.そのほかのシリコン・ダイはスレーブとしてマスタとだけ信号をやり取りする.DRAMメーカから見ると,マスタ・ダイとスレーブ・ダイを作り分けるというコスト増の要因はあるものの,電気的には入力容量と入力インダクタンスがシリコン・ダイ1個分にしかならないので,高速化に適している(図9).

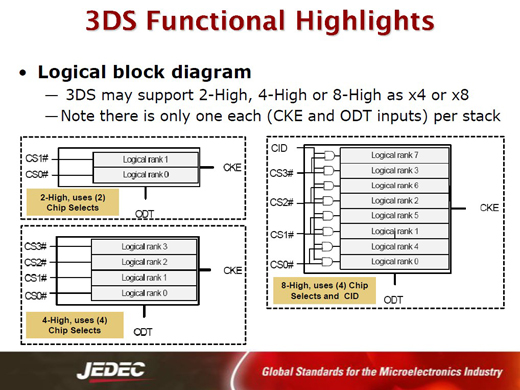

「3DS」の規格仕様では,シリコン・ダイを2枚積層した「2H(2-High)」,4枚積層した「4H(4-High)」,8枚積層した「8H(8-High)」の3種類のケースを想定する(図10).製品化は「2H」から始まる.またDDR4だけでなく,DDR3L(DDR3の低電圧版,電源電圧は1.35V)にも採用される可能性がある.

ふくだ・あきら

フリーランステクノロジーライター

http://d.hatena.ne.jp/affiliate_with/