次世代DRAM規格「DDR4」と新技術規格「3DS」の概要を公表 ―― Server Memory Forum 2011

半導体メモリの共通規格を策定している業界団体JEDECは2011年11月1~2日に,次世代DRAM規格の策定状況を説明する講演会「Server Memory Forum 2011」を米国カリフォルニア州Santa Claraで開催した(写真1).サーバおよびハイエンド・パソコン向けの次世代DRAM規格「DDR4」やDDR4モジュール規格,次世代マルチチップ・パッケージ技術「3DS」などの概要が紹介された.なお,これらの規格の内容は暫定的なものであり,2012年の正式公表時には一部が変更される可能性がある.

写真1 Server Memory Forum 2011の会場となったHilton Santa Clara

●DDR3の倍速,1.6Gbps~3.2Gbpsを担うDDR4

サーバやデスクトップ・パソコン,ノート・パソコンなどの主記憶(メイン・メモリ)には主に,「DDR3(Double Data Rate 3)」と呼ぶ規格に準拠したSDRAMとそのモジュールであるDIMM(Dual In-line Memory Module)が使われている.DDR3 DRAMは,クロック信号のエッジ(電圧上昇と電圧下降の両エッジ)に同期して8個のデータを内部であらかじめ読み出しておく(8nプリフェッチする)ことによって高速にデータを入出力している.例えばメモリ・クロックが200MHzのとき,データ入出力の速度は最大1.6Gbps(1端子当たり)に達する.

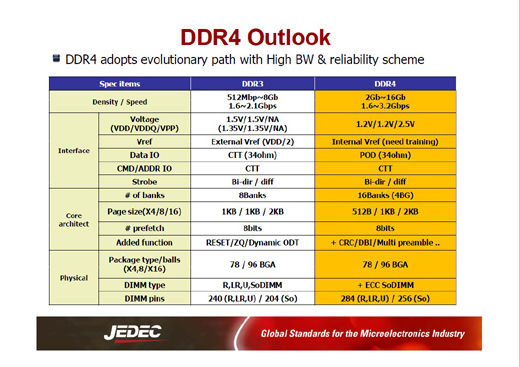

次世代のDRAM規格である「DDR4」では,8nプリフェッチとバンク・グループ切り替えにより,DDR3 SDRAMの2倍の高速動作を実現する(図1).

図1 DDR3 SDRAMとDDR4 SDRAMの主な仕様

※ クリックすると拡大できます

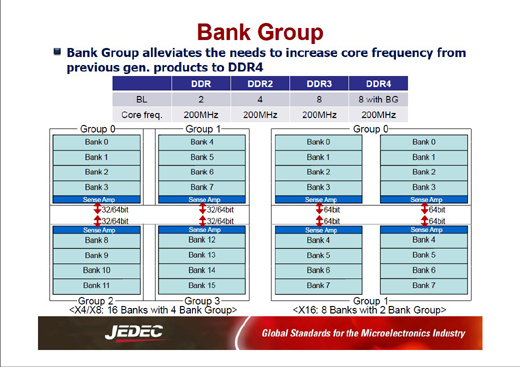

メモリ・セル・アレイを16個のバンクに分割し,4ユニット(×4ビット/×8ビット品)あるいは2ユニット(×16ビット品)のバンク・グループを構成する(図2).

図2 DDR4 SDRAMではバンク・グループ(Bank Group)を導入

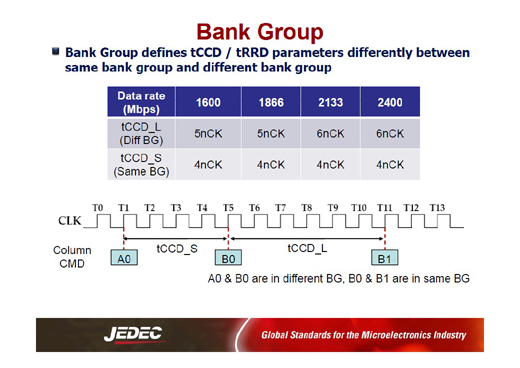

読み出しあるいは書き込みでは,異なるバンク・グループを連続してアクセスすると,実効的には16個のデータのプリフェッチ(16nプリフェッチ)と同じ速度が得られる.ただし同じバンク・グループを連続してアクセスした場合,動作速度はいくらか低下する(図3).16nプリフェッチを採用しなかったのは,シリコン・ダイ面積の増加(製造コストの増加)を嫌ったためである.

また消費電力(厳密にはデータ入出力速度当たりの消費電力)を低減するために,電源電圧をDDR3の1.5Vから,DDR4では1.2Vに下げている.電源は3種類を必要としており,コア電源が1.2V,入出力電源が1.2V,ワード線駆動用電源が2.5Vとなる.DDR3との大きな違いは,ワード線駆動用電源ピンを設けたことだ.DDR3まではワード線駆動用に高めの電圧を内部昇圧回路で発生させていた.内部昇圧回路による消費電流を削るため,DDR4では外部電源を別に設けることにした.

データ入出力線の終端手法にも違いがある.DDR3ではデータ・バスをCTT(Center Tap Terminated)インターフェースとしているが,DDR4ではPOD(Pseudo Open Drain)インターフェースとなる.PODだと出力がゼロ(論理値が「低」)のときにだけ電流が流れる.そこでDDR4では,出力にDBI(Data Bus Inversion)ビットを付加して8ビット並列バス出力の中で「ゼロ」を出力するビットを,DBIビットを含めて4ビット以下に抑え,消費電力を低減している.