Rambus,1レーン当たり5G~6.25Gbpsの第2世代PCI Expressに対応した高速シリアル伝送IPコアを開発中 ――Rambus Developer Forum Japan 2004

2004年7月8日~9日,グランドハイアット東京(東京都港区)にて,米国Rambus社の日本法人であるラムバス主催の「Rambus Developer Forum Japan 2004」が開催された.本フォーラムでは,PCI ExpressなどのI/Oインターフェースや,メモリ・インターフェースなどについての講演やセミナが行われた.ここでは,同社のVice President Corporate MarketingであるRonald N. May氏に,同社のIPコアや要素技術などについて話を聞いた(写真1).

[写真1] Rambus社のVice President Corporate MarketingであるRonald N. May氏

――貴社のIPコア製品の現状を教えてください.

Ronald N. May氏:現在,当社のIPコア製品は大きく,「メモリ・コア」と「ロジック・コア」に分類できます.メモリ・コアとしては,RDRAM(Rambus DRAM)や,RDRAMの8倍の伝送速度を実現するXDR DRAM(開発コード・ネーム「Yellowstone」)など,当社独自のバス・アーキテクチャを採用した製品があります.また,最近では,顧客からの強い要望により,DDR(double data rate)SDRAMも扱うようになりました.DDR SDRAMについては,メモリ・コアそのものではなく,メモリ・コントローラのIPコアを提供しています.

一方,ロジック・コアとしては,PCI ExpressなどのI/Oインターフェースのコアが挙げられます.最大6.4Gbpsの伝送速度を実現するパラレル・バス「Redwood」もその一つです(写真2).RedwoodはHyperTransportインターフェースに対応できます.そのため,ユーザからは,例えばRedwoodとPCI Expressのデュアル・モードをサポートしたインターフェース・コアを作ってほしいという声も聞かれます.このような製品を使用すれば,米国AMD社のCPUと米国Intel社のCPUの両方に対応できます.

また,当社はIPコアだけでなく,顧客の要求に応じてパッケージ設計やプリント基板設計など,システム(最終製品)の構築に必要な技術を提供しています.

(a) デモンストレーション・ボード

(b) チップ間の配線

[写真2] Redwoodのデモンストレーション

XDR DDRと同じく,ハンドシェイクにFlexPhase技術を採用している.本技術を用いると,配線長をそろえる必要はない(写真(b)).本デモンストレーションはテスト・チップに電気的な信号を与えて,データの転送を行った.伝送速度は6.4Gbps.

――最近,PCI Expressに関連するLSIが続々と登場しているようですが....

Ronald氏:一つの大きな要因として,米国Intel社がPCI Expressに対応したデスクトップ・パソコン向けのチップセットを発表したことが挙げられるでしょう.この発表で各メーカが勢いづいたのだと思います.

――高速シリアル伝送技術「RaSer」のPCI Express製品への採用状況は?

Ronald氏:「RaSer」は,PCI ExpressだけでなくGビットEthernetやSerial ATA,などさまざまな高速シリアル通信に対応する技術です.現在,RaSerのライセンス供与先は約25社ですが,そのうちの数社,例えば米国S3 Graphics社や台湾のALi社などはPCI Express製品に採用すると発表しています.

現状のRaSerは1Gbps~3Gbpsの伝送速度に対応していますが,ロードマップでは,5Gbps~6Gbpsに対応する「RaSer V」や10Gbps~12Gbpsに対応する「RaSer X」の製品化を予定しています.伝送速度が上がるのにつれて,配線の表皮効果やシンボル間干渉,ビアによるスタブの影響など,従来は考慮する必要のなかった問題が顕在化します.RaSer VやRaSer Xでは受信/送信側で適切なイコライゼーション(等化)を施すなどして,こうした問題に対応します.

また,RaSer Vをベースとして,次世代のPCI Express規格に対応する「Turbo PCIe PHY Platform」も開発しています(写真3).第2世代のPCI Expressでは,1レーン当たりの伝送速度が5Gbpsまたは6.25Gbpsになると言われています.正式な仕様が公開されしだい,本プラットホームもその規格に準拠した形で発表する予定です.

(a) デモンストレーションのようす

(b) 伝送速度2.5Gbps,イコライゼーション3dB

(c) 伝送速度5Gbps,イコライゼーションなし

(d) 伝送速度5Gbps,イコライゼーション3dB

(e) 伝送速度5Gbps,イコライゼーション4.7dB

(f) 伝送速度6.25Gbps,イコライゼーション6dB

[写真3] 次世代PCI Express規格を視野に入れた「Turbo PCIe PHY Platform」のデモンストレーション

高速シリアル伝送に関する新技術「Raser V」をベースにしたTurbo PCIe PHYコアのテスト・チップ(130nmプロセス,UMCで製造)を使って,2.5Gbps,5Gbps,6.25Gbpsのデータ転送が行われた.システム・クロックは125MHz.全長23インチ(ライン・カードを含む)のXAUIバックプレーンを介して転送を行った.現状のPCI Express規格では1レーン当たり2.5Gbpsであり,イコライゼーション(等化)は3dBと規定されている.しかし,伝送速度が上がるとイコライゼーションを強化する必要がある.Raser Vでは,イコライゼーションを調整することで,PCI Expressの次のバージョンの伝送速度であるとみられる6.25Gbpsでもきれいなアイ・ダイヤグラムを実現できる.

――PCI Expressについては,図研などとの提携を発表しています.

Ronald氏:現在,PCI Express関連で協力関係を結んでいるのは図研だけではありません.図研のほかに,フランスのPLD Applications社,米国Mentor Graphics社,米国Synopsys社とPCI Expressの開発プラットホームについて協力することを発表しています.当社は,ロジックIPコアのベンダに対して広く間口を開いており,機会があれば,さらにさまざまなベンダと協力関係を築いていきたいと考えています(写真4).

[写真4] 図研の「Z-Core PCI Express」のデモンストレーション

「Z-Core PCI Express」は,PCI ExpressのMAC層,データリンク層,トランザクション層に対応したIPコアである.デモンストレーションでは,物理層処理はRambus社の「Raser」を使用した.2004年4月に開催された「Intel Developer Forum Japan Spring 2004」でも同様のデモンストレーションが行われたが,そのときはケーブル長が50cm,伝送速度は1.8Gbps程度だった.今回はクロックのジッタを調整することでケーブル長を1mとし,かつ伝送速度も仕様どおりの2.5Gbpsを実現したという.

――XDR DRAMの優位点は何でしょうか.

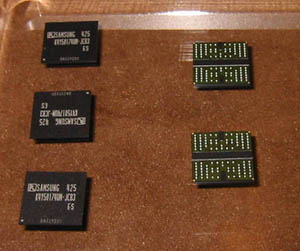

Ronald氏:XDR DDRは,1クロックで8ビット転送可能なODR(Octal Data Rate)技術を採用しており,従来のRDRAMに比べて8倍の伝送速度を実現できます.現在は3.2GHz(Gbps)のサンプル・チップが東芝や韓国Samsung社から出荷されていますが,ロードマップとしては最大6.4GHzまで対応する予定です(写真5).

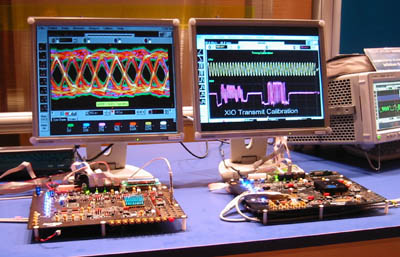

こうした高速伝送は,おもにグラフィックス処理や次世代のゲーム機などに応用されるでしょう.来年(2005年)にはXDR DDRを搭載したシステムが出荷されると考えています.しばらくの間は,DDRやGDDRと共存すると思いますが,今後,ゲーム機などに求められる性能を考えると,徐々にXDR DDRに移行していくと思います(写真6).

――XDR DDRに採用された「FlexPhase」技術について教えてください.

Ronald氏:FlesPhaseとは,ピンごとに位相を調整する技術です.複数のDRAMが接続されている場合でも,各DRAMでクロック・エッジが立つとデータを読み込むようにコントローラで制御します.本技術は,メモリ・コントローラに組み込みます.XDR DDRは差動信号を用いますが,従来,差動ペアでは線間のスキューを抑えるために,等長配線を施す必要がありました.しかし,本技術を用いるとその必要がなくなり,配線の自由度が高くなります.

[写真5] Samsung社のXDR DDR

韓国Samsung社は,2004年の初めに512MビットXDR DDRのサンプル出荷を開始した.伝送速度は3.2Gbps.XDR DDRについては,東芝が2003年末にいち早くサンプル出荷を開始している.Samsung社は,2004年末あたりから,まず256MビットのXDR DDRの量産出荷を開始する予定.

[写真6] XDRとDDRのMulti modeインターフェース・コントローラ

インターフェース(XIO /DDR Interface)部のプログラムを書き換えることにより,DDR,GDDR,XDRの各DRAMに対応できる.機種によってDDR SDRAMとXDR DDRなどを使い分けるような用途を視野に置いている.デモンストレーションでは,プログラムの書き換えによって,同じチップをDDR用(写真左)とXDR用(写真右)のコントローラとして利用していた.