Freescaleが新しいCortex-A9マルチコア・プロセッサやCortex-M4マイコンについて解説 ―― Freescale Technology Forum(FTF)Japan 2011

米国Freescale Semiconductor社の日本法人であるフリースケール・セミコンダクタ・ジャパンは,顧客向けの講演会兼展示会「Freescale Technology Forum(FTF)Japan 2011」を2011年9月13日に東京で開催した(写真1).Freescale社は毎年,世界各地域で顧客向けの講演会兼展示会「Freescale Technology Forum(FTF)」を開催してきた.日本では毎年9月に,日本法人のオフィスに隣接した目黒雅叙園(東京都目黒区)を会場としてFTF Japanを開催するのが恒例だった.北村 俊之 氏のレポートにもあるように,昨年(2010年)も目黒雅叙園でFTF Japan 2010が催された.

写真1 Freescale Technology Forum(FTF)Japan 2011の来場者登録受け付け所

●技術講演と展示会を重視したプログラムに変更

ところが今年(2011年)のFTF Japanは,いくつかの点で大きな変更があった.まず,会場がザ・プリンス パークタワー東京(東京都港区)の宴会場フロアに変わり,会場の面積が大幅に拡大された.技術講演のセッション数は2010年が24セッションだったのに対し,2011年は50セッションと2倍以上に増えた.この結果,10本の講演が同時に実施されるという大規模な講演会となった.

講演スケジュールも大きく変わった.前回までは午前中が基調講演を含む全体講演,午後がテーマ別のトラックに分かれて技術講演,というのが大まかなスケジュールだった.ところが今回は,午前~午後に技術講演トラック,夕方に基調講演という逆のスケジュールとなった.

また併設の展示会(FTF Japanでは「テクノロジ・ラボ」と呼んでいる)の開催時間も変更された.前回までは午前の基調講演が終了した段階で展示会がオープンし,夕方までずっと続くというものだった.オープンする時間はおおよそ午前11時30分である.

これに対して今年は受け付け開始時間の午前9時には展示会がオープンし,受け付けを済ませた来場者はまず展示会場に案内される,という仕組みになった(写真2).そして展示会場は夕方の基調講演に合わせて午後3時半~午後5時半の間に閉鎖され,基調講演が終わると懇親会を兼ねた会場として再びオープンする,というスケジュールとなった.

写真2 FTF Japan 2011の展示会場

全体としては技術講演の本数を倍増し,展示会場の滞在時間を長く確保したことになる.その一方で基調講演および全体講演の時間は前回に比べると短縮された.来場者の大半がエンジニアであることを考慮して,イベントの性格を実務寄りにずらしたことがうかがえる.

●4個のARMコアを内蔵する「i.MX6」プロセッサの概要を公表

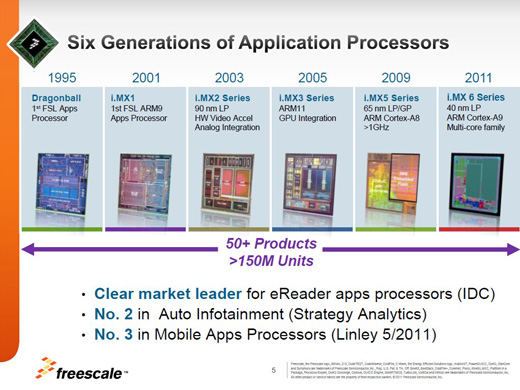

技術講演の大きな話題は,ARMコア内蔵のマルチメディア・プロセッサ「i.MX」の最新版である「i.MX6シリーズ」の概要が公表されたことだ(講演番号FTF-CON-1166).i.MXプロセッサはこれまでに50品種を超える製品が開発されており,累計で1億4500万個を超えるチップが出荷されたと説明していた(図1).

図1 「i.MX」プロセッサの歴史(このスライドはFTF Indiaで発表されたもの)

※ 図をクリックすると拡大します

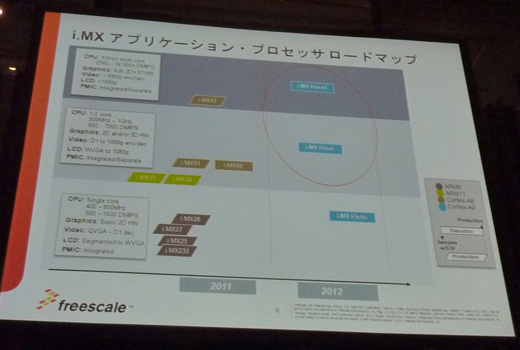

i.MX6は,i.MXプロセッサとしては6世代目に相当するシリーズである.最大の特徴は,ARMアーキテクチャの高性能コア「Cortex-A9」を内蔵することと,初めてマルチコア構成となったことだ.さらに詳しく説明すると,Cortex-A9コアを4個内蔵する「i.MX 6Quad」と,Cortex-A9コアを2個内蔵する「i.MX 6Dual」,シングル・コアの「i.MX 6Solo」の製品化が予定されている.最も早く市場に投入されるのは4コア(クァッドコア)の「i.MX 6Quad」と2コア(デュアルコア)の「i.MX 6Dual」で,2012年前半にサンプル出荷が始まる予定である(写真3).

写真3 「i.MX6シリーズ」の製品化計画

※ 写真をクリックすると拡大します

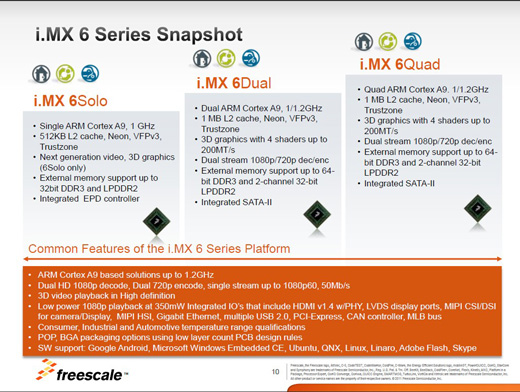

i.MX 6シリーズは,いずれも動作周波数が最大1.2GHzのCortex-A9コアを内蔵する.2次キャッシュはシングル・コア品が512Kバイト,2コア/4コア品が1Mバイト(共有キャッシュ)である.DSPコアのNEONプロセッサ・コア,セキュリティ機能のTrustZoneをCPUコアに搭載している(図2).

図2 「i.MX6シリーズ」の品種と製品概要(このスライドはFTF Indiaで発表されたもの)

※ 図をクリックすると拡大します

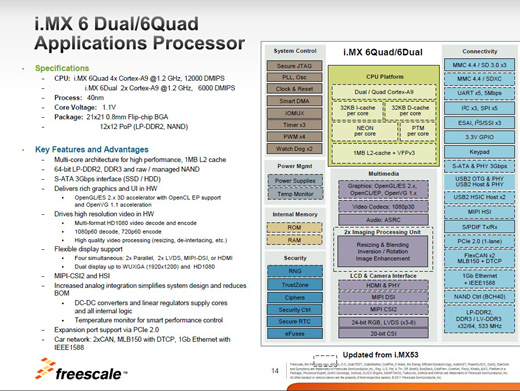

講演では,2コアの「i.MX 6Dual」と4コアの「i.MX 6Quad」の内容を主に説明した(図3).i.MX 6Dualの最大性能は6000DMIPS(Dhrystone MIPS),i.MX 6Quadの最大性能は12000DMIPSである.製造技術は40nmプロセス.電源電圧(コア電圧)は1.1V.パッケージは21mm角のフリップチップBGA,あるいは12mm角のPoP(Package on Package)である.PoPの場合はLP-DDR2 SDRAMとNANDフラッシュ・メモリが載る.

図3 2コア品「i.MX 6Dual」と4コア品「i.MX 6Quad」の内部ブロック(このスライドはFTF Indiaで発表されたもの)

※ 図をクリックすると拡大します

周辺回路はきわめて豊富で,多種多様な機能を内蔵する.DRAMコントローラは64ビット幅のLP-DDR2とDDR3,DDR3Lをサポートする.ストレージはNANDフラッシュ・メモリ(40ビットのBCH誤り訂正対応),Serial ATA 3Gbps,MMC4.4/SDXCに対応する.ディスプレイはHD1080pの2チャネル出力である.ネットワーク・インターフェースはUSB 2.0ホスト,MIPI HSI,PCI Express 2.0(1レーン),FlexCAN(2チャネル),ギガビットEthernet(IEEE 1588対応)などを備える.

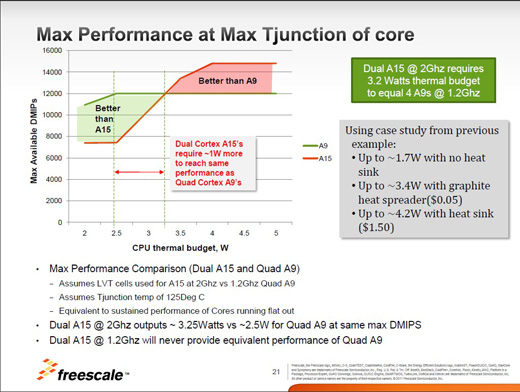

マルチコア化による最大の恩恵は,当然のことだが,同じ演算性能を実現したときの消費電力の低減である.12000DMIPSを実現するときの消費電力は,同じCortex-AシリーズのCPUコアで比較すると,2コアのCortex-A15が3.25W(動作周波数2GHz)になるのに対し,4コアのCortex-A9では2.5W(動作周波数1.2GHz)で済むという(図4).

図4 2コアのCortex-A15プロセッサと4コアのCortex-A9プロセッサの消費電力(このスライドはFTF Indiaで発表されたもの)

※ 図をクリックすると拡大します

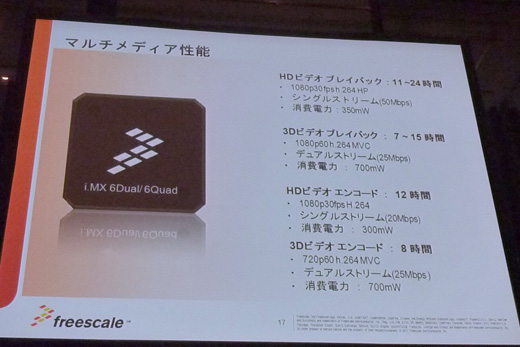

この結果,i.MX6シリーズでは高いマルチメディア処理性能と低い消費電力を両立させている(写真4).例えばH.264 HPの1080pビデオ・ストリーム(30フレーム/s)を再生したときの消費電力は350mW,1080pビデオ・ストリーム(30フレーム/s)をH.264に符号化(エンコード)したときの消費電力は300mWである.

写真4 i.MX6のマルチメディア性能(消費電力)

※ 写真をクリックすると拡大します