AMDが性能で妥協しないノート・パソコン用CPUコア「Bobcat」を公表 ―― Hot Chips 22

2010年8月22日~24日,高性能チップに関する技術講演会「Hot Chips(A Symposium on High Performance Chips)」が米国カリフォルニア州Palo AltoのStanford Universityで開催された(写真1).米国AMD(Advanced Micro Devices)社がノート・パソコン用の次世代CPUコアとサーバ用の次世代CPUコアの技術概要を明らかにしたほか,米国Intel社が32nm世代のマルチコアCPUの技術概要を発表した.

写真1 Hot Chipsの会場であるStanford UniversityのMemorial Auditorium(米国カリフォルニア州Palo Alto)

●アウト・オブ・オーダ実行機能を装備

AMD社が公表したノート・パソコン用の次世代CPUコアは,開発コード名「Bobcat(ボブキャット)」として知られる(写真2).講演者は,AMDフェローでBobcatコアのチーフ・アーキテクトを務めるBrad Burgess氏である.

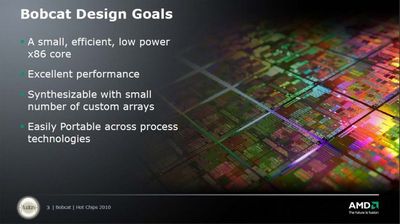

写真2 ノート・パソコン用次世代CPUコア「Bobcat」の設計目標

Bobcatは,x86命令セット・アーキテクチャ互換のCPUコアで,ノート・パソコンでもローエンドの低消費電力品に向けたものである(写真3).Intel社のネットブック/モバイル用x86プロセッサ「Atom」に対抗するプロセッサのCPUコアとも言われているが,Bobcatの高性能化技術はAtomよりも豊富で,ネットブックより上位でノート・パソコン全体では下位に位置するパソコンおよびモバイル機器を受け持つように見える.

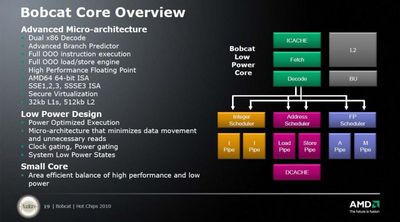

写真3 Bobcatコアの概要

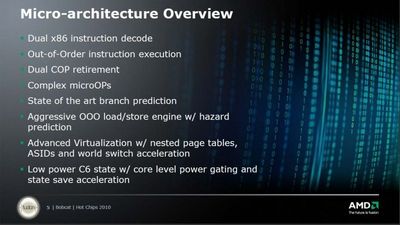

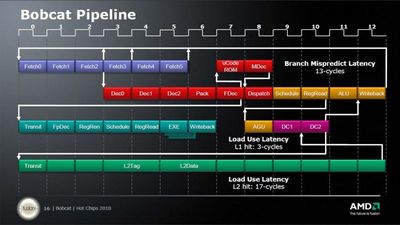

すなわち2命令同時発行はAtomと同じだが,アウト・オブ・オーダ実行機能や最新の分岐予測機構など,Atomが実装していない手法を,Bobcatは採用している(写真4,写真5).また,64ビットの命令セットであるAMD64を搭載していることも,Atomと大きく違う.Bobcatを載せたマシンはAtomマシンとは違い,高性能な64ビットOSを実装できる.

写真4 Bobcatのマイクロアーキテクチャ(概略)

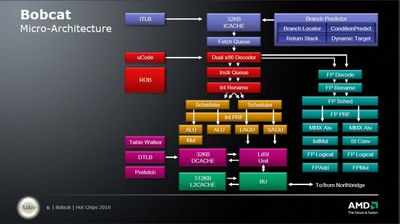

写真5 Bobcatのマイクロアーキテクチャ(フローチャート)

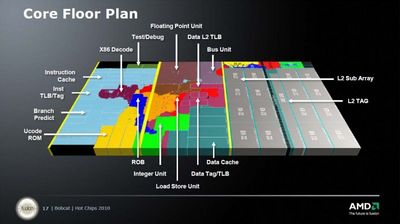

演算ユニットは整数演算ユニットと浮動小数点演算ユニットを装備する.1次キャッシュは命令32Kバイト,データ32Kバイト.2次キャッシュは512Kバイトである.消費電力を低減するため,CPUコアごとに電源を遮断するパワー・ゲーティングを備える(写真6,写真7).

写真6 Bobcatのパイプライン構成

写真7 Bobcatをシリコンにレイアウトしたときのフロア・プラン

tag: CPU

Post a Comment