AMDが性能で妥協しないノート・パソコン用CPUコア「Bobcat」を公表 ―― Hot Chips 22

●デュアルコアを基本構成とするマルチコアCPU

AMD社が公表したサーバ用の次世代CPUコアは,開発コード名「Bulldozer(ブルドーザ)」として知られている(写真8).講演者は,AMDフェローでBulldozerコアのチーフ・アーキテクトを務めるMike Butler氏である.

写真8 BulldozerコアとBobcatコアの位置付け

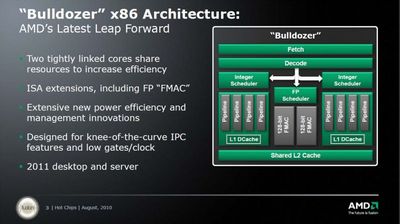

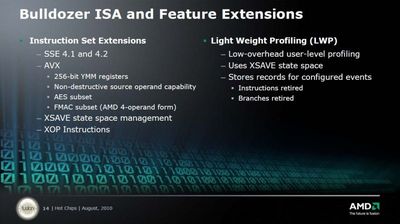

Bulldozerコアは,2個以上のCPUコアを内蔵するマルチコア構成を前提に設計されている.内蔵するCPUコアの数を2個ずつ増やすことで,消費電力の急増を防ぎながら演算処理性能を高めていく(写真9).言い換えるとBulldozerコアは,デュアルコアが基本構成となっている.デュアルコアの各コアが整数演算器と1次命令キャッシュ,1次データ・キャッシュを供えており,1個のスレッドを実行する.浮動小数点演算器(2個の128ビット積和演算器を内蔵)と2次キャッシュは,2個のCPUコアで共有する(写真10).

写真9 Bulldozerコアのx86アーキテクチャ

写真10 Bulldozerコアの機能拡張部分

●10コアを内蔵する32nm世代のx86系マイクロプロセッサ

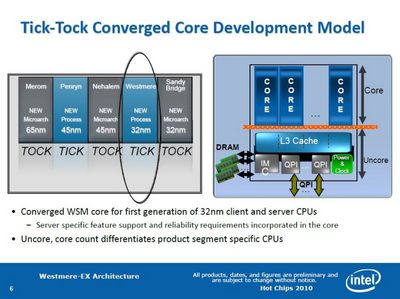

Intel社は,サーバ用およびデスクトップ・パソコン用のマイクロプロセッサ開発で,「Tick-Tock(チックタック)」と呼ぶ開発方針を採用し続けてきた(写真11).半導体製造技術の微細化とCPUコアのアーキテクチャ開発を交互に実行するという方針である.例えば製造技術を65nm世代から45nm世代に微細化するときは,CPUコアはアーキテクチャを維持しながら縮小する.これが45nm世代での最初のマイクロプロセッサ製品(45nmの第1世代品)となる.これを「Tick」と呼ぶ.それから製造技術をそのままに,CPUコアのアーキテクチャを変更したマイクロプロセッサを開発し,製品化(45nmの第2世代品)する.これを「Tock」と呼ぶ.

写真11 Intel社のマイクロプロセッサ開発方針

Intel社は45nm世代の「Tock」に相当する「Nehalem(ネハーレン)」アーキテクチャのマイクロプロセッサ群を開発し,製品化してきた.32nm世代の「Tick」に相当するマイクロプロセッサ群には「Westmere(ウエストミア)」の開発コード名が与えられており,すでにデュアルコア版,4コア版,6コア版が製品化されている.

Hot Chips 22では,10個のCPUコアを内蔵する32nm世代のマイクロプロセッサ「Westmere-EX」の概要が公表された.講演者はWestmere-EXのアーキテクチャ開発を担当しているDheemanth Nagaraj氏とSailesh Kottapalli氏である.

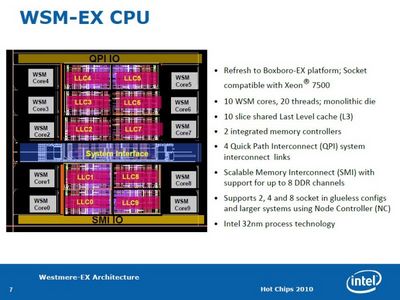

「Westmere-EX」は各コアが最大2個のマルチスレッディングを実行できる10個のCPUコアを内蔵しており,全体で最大20個のスレッドを同時並行で処理する(写真12).8個のCPUコアを内蔵するNehalemプロセッサ,製品名「Xeonプロセッサ7500番台」とソケット互換である.

写真12 Westmere-EXの概要とチップ・レイアウト

CPUコアは,コアごとに1次キャッシュと2次キャッシュを搭載している.シリコン・ダイとしては各CPUコアが共有する3次キャッシュも内蔵する.この3次キャッシュは10個のスライスと呼ぶブロックに分かれており,各スライスをリング状の双方向バスで接続することでスライス間の高速データ転送を実現している.

Westmere-EXの入出力インターフェースは4本のQPI(Quick Path Interconnect)である.QPIを介して複数のWestmere-EXチップを相互接続することで,マルチプロセッサ構成の高性能サーバ・システムを構築できる.

tag: CPU

Post a Comment