FPGAを使った数値演算回路実現の勘所(3) ―― 浮動小数点演算器の構成を考える Part 1

●加減算回路の演算手順

加減算回路について説明します.

乗算,除算の演算については,仮数部はけたを合わせることなく直接の演算が可能で,けたを合わせるのは指数部の担当でした.しかし加減算については,仮数部を加減算する時点でけたを合わせておかないと,演算そのものが成立しません.指数部が異なる2数どうしでは,真の小数点位置が異なるわけで,直接加減算できないということです.従って,2数のどちらか一方の指数部を他方の指数部と同じとなるように,仮数部をシフト・アップ/ダウンしてやる必要があります.

実際には,絶対値の大きい方を基準とし,絶対値の小さい方の指数部を大きい方と同じにして,仮数部をダウン・シフトすることでけたを合わせる,という方法が採られます.ダウン・シフト量は2数の指数部の差分になり,絶対値の小さい方の指数部に加算してつじつまを合わせます.当然,絶対値の小さい方の仮数部には,ulp未満にけたが発生するので,そのまま加減算してしまうと,無用に大きなけたの加減算となってしまいます.絶対値の大きい方から見れば,そこは有効けた外なので意味を持ちません.

これを避けるため,絶対値の小さい方の仮数部のulp未満によりG,R,Sビットを生成し,ulp未満は3けたとして演算します.

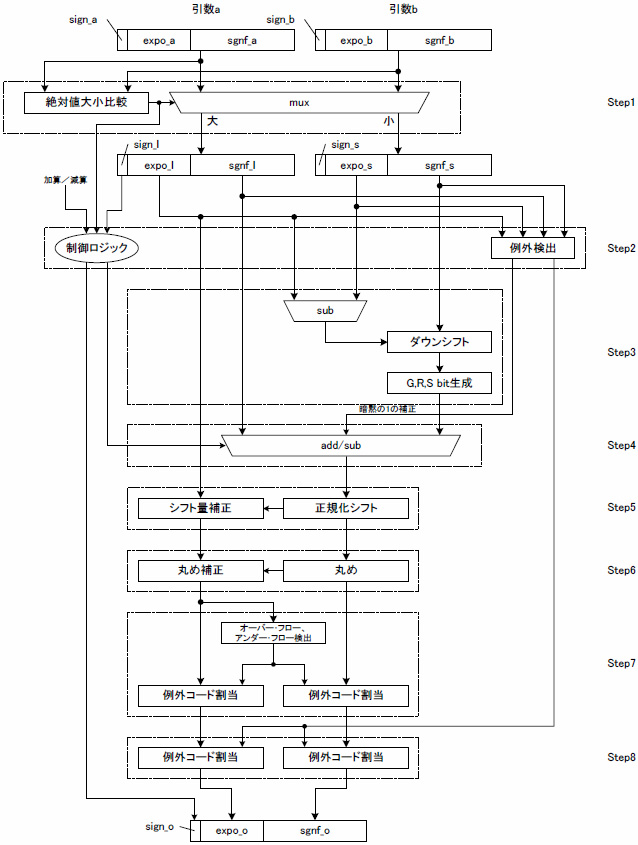

以上の方法を適用した手順は以下のようになります.

Step 1. 2数の絶対値を比較し,大側,小側を決める

Step 2. 例外検出(指数部=0または255,仮数部=0)

Step 3. 大小2数の指数部の差分を演算し,小側をダウン・シフト.G,R,Sビットを生成する(前シフト)

Step 4. 加減算(仮数部の加減算のみ)

Step 5. 正規化

Step 6. 丸め

Step 7. オーバフロー,アンダフローによる例外コード割り当て

Step 8. 初期状態の例外検出による例外補正

これらの手順によるブロック図を,図5に示します.実際に加減算を行っているのはStep 4のみですが,周辺にはたくさんの操作が必要になります.

図5 浮動小数点加減算のブロック図

加減算においては,正規化(Step 5)においても乗除算と差があります.Step 4で仮数部同士で減算が行われた場合,減算結果の上位のほとんどが0になってしまう場合があります.乗除算では最上位を見れば正規化できたのですが,加減算では全けたを見たうえで正規化する必要があります.

* * *

駆け足で,浮動小数点演算回路の基礎について説明しました.どうでしょうか.浮動小数点演算は,四則演算だけとっても大変面倒で,固定小数点演算のようにはいかないことが分かりました.これだけで浮動小数点演算を避ける立派な理由になってしまいますね.

しかし,どうしても使わなければならない場合だってあるわけです.どうしたらよいのでしょう.これについては,次回に説明します.

●参考文献

(1) 鈴木 昌治;ディジタル数値演算回路の実用設計,CQ出版,2006年.

(2) デイビッド・A. パターソン,ジョン・L. ヘネシー;コンピュータの構成と設計 第2版(上),日経BP社,1999年.

(3) 小林 芳直;浮動小数点演算回路を極める,pp.44-56,Design Wave Magazine 2003年7月号,CQ出版.

すずき・しょうじ