FPGAを使った数値演算回路実現の勘所(3) ―― 浮動小数点演算器の構成を考える Part 1

●除算回路の演算手順

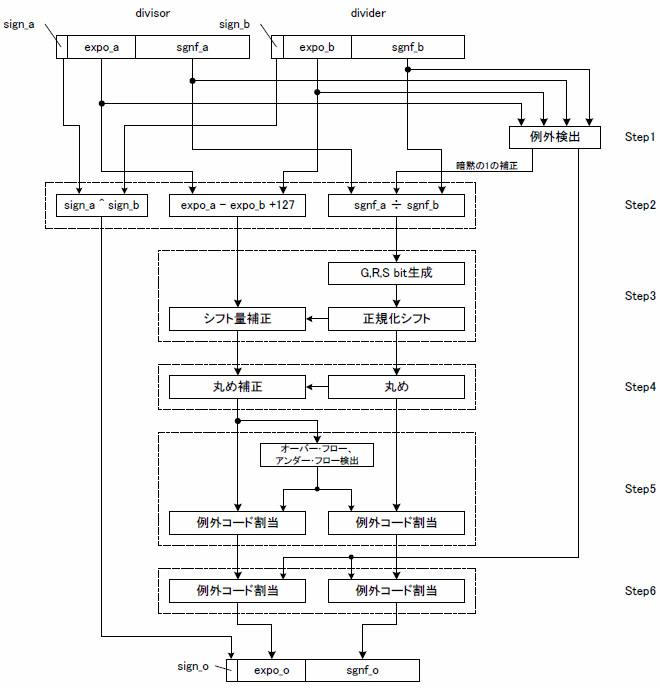

次に,除算回路の演算手順を説明します.

Step 1. 例外検出(指数部=0または255,仮数部=0)

Step 2. 除算(符号のEXOR,指数部の減算,仮数部の除算)

Step 3. 最上位けたによる正規化

Step 4. 丸め

Step 5. オーバフロー,アンダフローによる例外コード割り当て

Step 6. 初期状態の例外検出による例外補正

これらの手順によるブロック図を,図4に示します.実際に除算を行っているのはStep 2のみで,乗算と異なるのもこの部分のみです.

図4 浮動小数点除算のブロック図

また,G,R,Sビットの生成で若干の違いがあります.例えば単精度乗算の場合,仮数部は24ビットの乗算になるので結果は48ビットとなり,これが演算によって求められるすべてのけたなので,これに対して丸めを行うことになります.しかし除算では,どのけたまで求めるかは設計者が決めることで,自動的に決まるものではありません.必要なけたまで求めるのはもちろんですが,例えばSビットを決めるために商を何けたまで求めてからORするか,というのは悩ましい話です.

原理については省略しますが(参考文献(1)に説明があるので,参照されたい),仮数部の本体24ビット+G,Rビットまで商を求めて,無条件にSビット=1とすれば,正しい丸めへの準備ができると考えてください.これはあくまでも図4におけるStep 2のG,R,Sビットの生成の場合となります.

これ以降,Step 4までは乗算と全く同じで,問題ありません.Step 5では,初期状態における例外条件によって,割り当てる例外コードが違ってきます.