FPGAを使った数値演算回路実現の勘所(1) ―― 加算器の構成を考える

3.FPGAで加算器の性能を検証

では,実際に加算器の回路構成によって,その遅延量がどのように変わるのかを検証してみましょう.

●四つの回路をSpartan-3に実装した場合で比較

あくまでも回路方式による比較なので,デバイスは1種類に限定することとします.やはり,筆者の手慣れたところでXilinx社のSpartan-3ファミリを採用し,プロジェクトを新規作成する際にデフォルトで登場した「XC3S50-5-PQ208」を選択しました.それ以外に他意はありません.

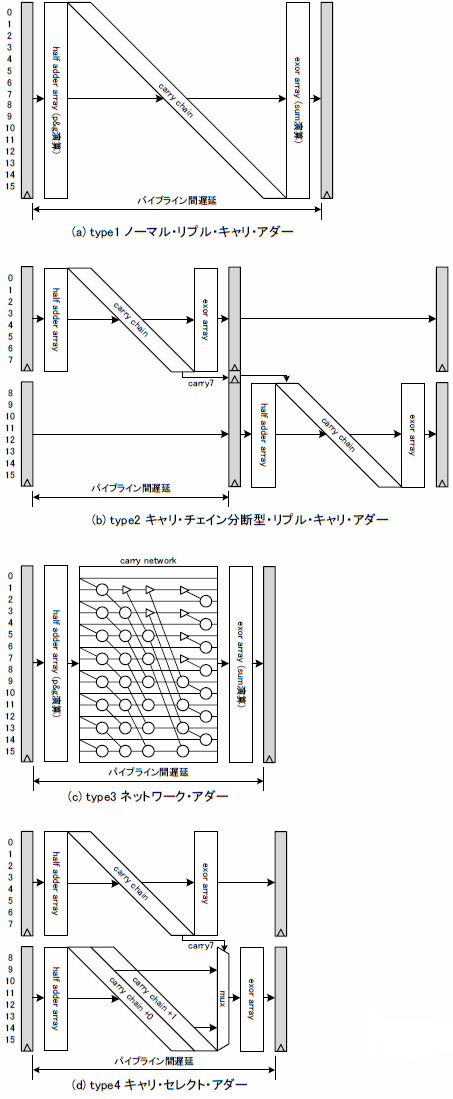

Xilinx社の論理合成ツール(XST)を用い,論理合成結果におけるタイミング見積もりによってパイプライン間の遅延を比較します.比較する加算器のビット幅は16ビットとし,以下の4種類を選択しました.図6にそれぞれの構成を,遅延を考慮したブロック図で示します.

図6 比較に使用した加算器の構成

1) ノーマル・リプル・キャリ・アダー(type 1,図6(a))

単純にout=a+b と記述し,XSTまかせで論理合成します.先に説明したリプル・キャリ・アダーが出来上がります.キャリ・チェーンは16ビットの長さになります.

2) キャリ・チェーン分断型リプル・キャリ・アダー(type 2,図6(b))

16ビットを8ビットで二つに分断し,下位の8ビット加算が終了したところで1度パイプライン・レジスタを挿入します.その後,上位8ビットの加算を行って,さらにパイプライン・レジスタを挿入し,2段のパイプラインとします.キャリ・チェーンが2分されることになりますので,加算器における遅延の要が半分となった効果を観察します.

3) ネットワーク・アダー(type 3,図6(c))

Alternative-Parallel-Prefix-Network-Adderの代表としてBrent-Kung/Kogge-Stoneスタイルのキャリ・ネットワークを採用し,ネットワーク・アダーがFPGAに対して有効かどうかを確認します.記述は,AND,OR,EXOR程度の論理記述を組み合わせたゲート・レベルの記述となっています.

4) キャリ・セレクト・アダー(type 4,図6(d))

type 2のキャリ・チェーン分断型リプル・キャリ・アダーでは,キャリ・チェーンを上下2段に分断したことで,パイプラインが2段になってしまいます.仕様としてこれが許されない場合,キャリ・セレクト・アダーを使用すると,上位/下位で独立のキャリ・チェーンを並列に構成できるので,キャリ・チェーンの長さを半分に保ったままパイプライン1段で構成可能となる場合があります.マルチプレクサが必要となり,その分の遅延は覚悟しなければなりませんが,昔のFPGAでは十分に効果を得ることができました.現在のデバイスで効果を検証します.