FPGAを使った数値演算回路実現の勘所(1) ―― 加算器の構成を考える

●Cyclone IIIのロジック・エレメントを見る

次に,Spartan-3と同じ低コスト・デバイスであるAltera社のCyclone IIIファミリを取り上げます.Cyclone IIIでも,加算器を実現する基本構成がリプル・キャリ・アダーであること,キャリ・チェーンを抜き出して専用ハードウェアとして高速化を徹底していることなどはSpartan-3と変わりません.汎用ロジックと共存させることを考えると,代表的な解はこのような構成になってしまうのでしょう.

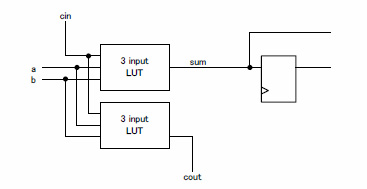

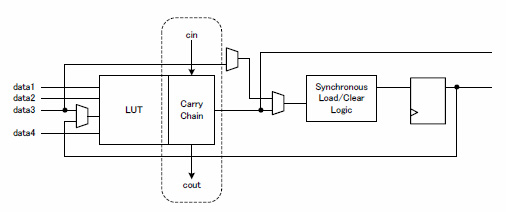

図4にCyclone IIIの「演算モード」時におけるロジック・エレメントの構成を示します.この図も加算機能に注目したうえで簡略化してあります.LUTを3入力2出力モードで使用し,フル・アダーを実現していると説明されてます.この図を見る限り,キャリ・チェーンは独立しておらず,LUT内部でキャリを生成しているかのように見えます.しかし,ロジック・エレメントの構成図(図5)を見ると,やはりキャリ・チェーンはLUT内部を通過せず,極力軽いロジックを専用ラインで通過していると推定されます.やはり,高速化のためには必要な措置と考えるべきでしょう(最大遅延を与えるパスのリストを見るとキャリ・チェーン演算を行う小さな遅延のゲートが配線遅延0でビット数分だけ連結しているのが確認できる).

図4 キャリ・チェーン周辺のロジック・エレメント(簡略図)

図5 ロジック・エレメント(簡略図)

Altera社の高性能デバイスであるStratix IVでは,ちょっと変わった機能が用意されています.ALM(Active Logic Module)内のLUTを4入力LUT×4として使用し,2ビットのキャリ・セレクト・アダー(キャリ信号が'0'の場合と'1'の場合の2通りの加算結果をあらかじめ計算し,キャリ信号が到着した時点でセレクタにより一方の結果を選択する方式)を構成できるのです.キャリ・セレクト・アダーは,ビット幅を大きくとるとセレクト信号の負荷が重くなってしまい,その効果が出にくいのですが,ビット幅を小さくすればその問題は解決します.また,専用のマルチプレクサを用意してしまうとゲート遅延と配線遅延が累積されて効果が薄れてしまいますが,キャリ・チェーンの中に同居させる形で作り込むことにより,効果を引き出していると推定されます.

以上のことから分かることは,FPGAベンダごとに工夫を凝らして,現在の高速な演算(加算)機能が実現できているということです.従って,「これを利用しない手はない」ということと,「構造には逆らわない方が良さそうだ」ということが想像できるわけです.