不揮発メモリや3次元LSIなどの研究成果を発表 ―― VLSI 2010レポート

半導体のデバイス技術とプロセス技術に関する最新の研究成果が披露される国際会議「Symposium on VLSI Technology」(VLSI Technology)と,半導体の回路技術に関する最新の研究成果が披露される国際会議「Symposium on VLSI Circuits」(VLSI Circuits)が,米国ハワイ州Honoluluでそれぞれ6月15日~17日と6月16日~18日に開催された(写真1).

VLSI TechnologyとVLSI Circuitは毎年6月に同じ会場で,日程を少しだけずらして開催されてきた.このため,両者をまとめて「VLSI XXXX」(XXXXは西暦)と総称することが多い.開催地は偶数年が米国のハワイ州Honolulu,奇数年が日本の京都となっている.2010年の今年はハワイ州Honoluluで開催された.

写真1 VLSI 2010の参加登録受け付けの様子

なお半導体の研究開発コミュニティでは,毎年12月に半導体のデバイス技術とプロセス技術に関する世界最大の国際会議IEDM(IEEE International Electron Devices Meeting)が,毎年2月に半導体の回路技術に関する世界最大の国際会議ISSCC(IEEE Internatinal Solid-State Circuits Conference)がそれぞれ開催されている.これらの2大イベントに比べるとVLSIは開催規模が小さいものの,プロセッサやメモリ,ロジックなどの開発動向をきちんと押さえておきたい技術者にとっては,ウォッチしておいた方がよい学会だ.

●Samsungが32nm NAND型フラッシュの微細化技術を発表

それではVLSI 2010の注目講演を紹介しよう.まずはNAND型フラッシュ・メモリ技術である.

韓国Samsung Electronics社は,1個のメモリ・セルに3ビットを記憶する3ビット/セル方式を採用し,線幅32nmと微細な加工技術で製造した32GビットNAND型フラッシュ・メモリ技術を発表した(VLSI Technology,講演番号12.1).この32Gビット・チップはすでに量産に入っているという(写真2~写真4).

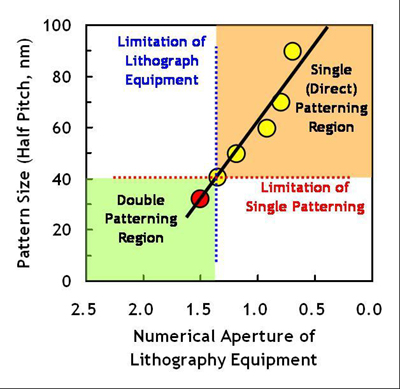

製造技術のポイントは,最も微細なパターン(ゲート電極)の加工に2重露光技術(ダブル・パターニング技術)を採用したことにある.現在の最先端露光技術はArF(フッ化アルゴン)レーザと液体浸漬露光技術の組み合わせを利用しているが,それでも開口数(N.A.)が1.4までの解像力となり,加工できる最も微細なパターンは線幅40nmになってしまう.線幅32nmなど,さらに微細なパターンを加工するには,露光と現像を2回繰り返す2重露光技術によって,実効的にN.A.を1.5くらいに上げなければならないとしていた.

ただし,2重露光技術を採用すると,製造のスループットが大幅に低下する.そこで,2重露光技術を導入するのは最小限度にとどめた.具体的にはゲート電極の加工だけに2重露光技術を採用し,ゲート電極と直交する拡散層(アクティブ・エリア)のパターン形成には通常の露光技術を使用した.こうすると拡散層に2重露光を採用した場合に比べてシリコン・ダイの面積が5%ほど大きくなるものの,従来の製造スループットが維持されるとともに,メモリ・セルの信頼性を確保しやすくなる.

写真2 半導体露光技術における解像度と開口数(Numerical Aperture)の関係

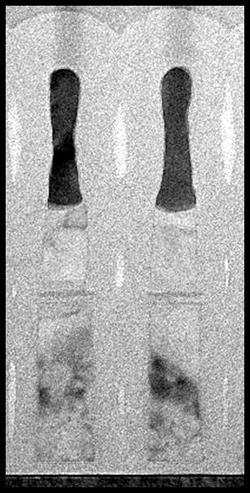

写真3 ゲート電極の断面を透過型電子顕微鏡で観察したところ

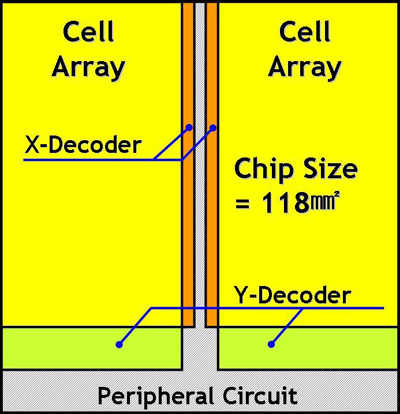

写真4 32GビットNAND型フラッシュ・メモリのレイアウト

シリコン・ダイの面積は118mm2(平方ミリ).

同社はまた,加工寸法が20nm以下のフラッシュ・メモリ・セル技術を発表した(VLSI Technology,講演番号12.2).フローティング・ゲート型のメモリ・セルを改良し,次世代のNAND型フラッシュ・メモリに適用できるようにするための開発努力の一環である.

フローティング・ゲート型メモリ・セルは,MOSトランジスタのゲート電極を2層の積層構造にしたメモリ・セルで,下層が電気的に浮遊したフローティング・ゲート,上層が制御ゲートとなっている.制御ゲートにある程度以上の電圧を印加することでフローティング・ゲートにシリコン基板から電子を注入し,MOSトランジスタのしきい電圧を変えることでデータを蓄える.

実際には,フローティング・ゲートは垂直に立った壁のようになっており,その周囲を絶縁膜である酸化窒化膜が覆い,その上に制御ゲートがかぶさっている.ここで問題となるのは,制御ゲートに電圧を印加するとフローティング・ゲートの頂上に存在する角の部分で,電界集中が発生することだ.電界集中によって電子の一部はフローティング・ゲートにとどまらず,制御ゲートに向かって飛び出してしまう.このため,データの書き込み効率が低下するほか,一部の電子が絶縁膜中に残って時間経過とともに制御ゲートに飛び込んでいくため,データ保持特性が劣化する.この電界集中は,微細化を進めるほどひどくなっていく.

そこでSamsung社は,フローティング・ゲートの頂上付近をシリコン窒化膜(絶縁膜)で覆うことにより電界集中を緩和した.シミュレーションでは,ピークの電界が20%ほど低くなったとしている.