不揮発メモリや3次元LSIなどの研究成果を発表 ―― VLSI 2010レポート

●相変化メモリの512Mビット品を試作

続いて相変化メモリ(PCM:Phase Change Memory)の話題である.PCMは,カルコゲナイドと呼ばれるGeSbTe合金(ゲルマニウム・アンチモン・テルル)が結晶状態(結晶相)とアモルファス状態(アモルファス相)の二つの状態(相)を往復する性質を利用したメモリで,二つの状態(相)が電源を切っても維持される不揮発メモリとなる.将来の大容量不揮発メモリの市場を狙った研究開発が活発に実施されている.

これまでに,Samsung社が512MビットのPCMチップを,米国Micron Technology社(元はNumonyx社,Micron社がNumonyx社を2010年2月に買収)が1GビットのPCMチップを学会発表したことがある.

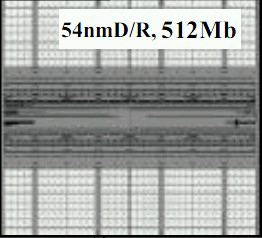

VLSI 2010では,韓国Hynix Semiconductor社が,512MビットのPCMを試作してみせた(VLSI Technology,講演番号19.1).設計ルールは54nmである.セル選択素子はダイオード.メモリ・セル・アレイは64Mビット×8バンク構成である(写真5).

講演では,隣接するメモリ・セル間での熱干渉とその対処方法を説明した.PCMではGeSbTe合金を加熱して冷却する条件を変えることで,結晶相あるいはアモルファス相を実現する.結晶相では電気抵抗が低く,アモルファス相では電気抵抗が高い.この電気抵抗の違いが,記憶するデータの違いとなる.ここで心配なのは,選択したメモリ・セルのGeSbTe合金をヒータで加熱するときに,熱伝導によって隣り合うGeSbTe合金も加熱される恐れがあることだ.

Hynix社は試作した512Mビット・チップを使い,加熱用電流パルスの波形やセル間の距離などを変えて熱干渉の様相を測定および観察した.そして熱干渉が発生しない条件を求め,16nmという微細な設計ルールでPCMセルを製造するときの条件に当てはめていった.例えばデータの書き込みと読み出しを隣り合うセルごとに順番に実行するのではなく,1個ずつ飛ばして実行することによって熱干渉を防いだ.

写真5 512MビットのPCMチップ

●異なる種類のデバイスを積層する「3次元LSI」

このほかVLSI 2010では,異なる種類のデバイスを積層する「3次元LSI」を開発する試みが目立っていた.

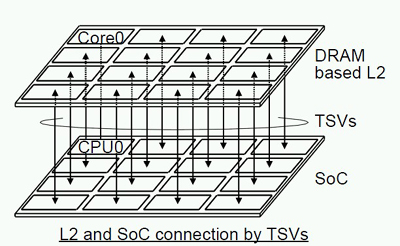

日立製作所は,DRAMのシリコン・ダイとCMOSロジックのシリコン・ダイの間を1Tバイト/sというきわめて高いデータ転送速度で接続するインターフェース技術を発表した(VLSI Circuits,講演番号18.1).DRAMのシリコン・ダイとCMOSロジックのシリコン・ダイは,シリコン貫通電極(TSV:Through Silicon Vias)で物理的および電気的に接続する(写真6,写真7).DRAMの記憶容量は1Gビット.

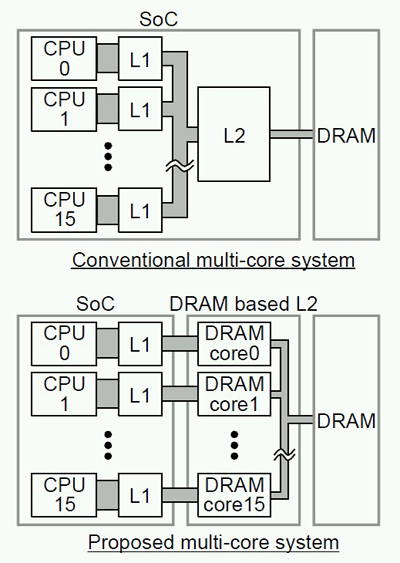

CMOSロジックは,16個のCPUコアを備えるマルチコア・プロセッサを想定した.各コアの2次キャッシュとして64MビットのDRAMが接続される.マルチコア・プロセッサと直結される1GビットDRAMは,16個の64Mビット・メモリ・セル・アレイ(「コア」と称している)で構成される.CPUコア当たりに8Mバイトの2次キャッシュを抱いた構成となる.

DRAMコアおよびCPUコア当たりのデータ入出力バスは32本で,これらは差動伝送である.DRAMコアの内部は四つのバンクに分かれており,各バンクをインターリーブして高速にデータをやりとりする.1本の入出力バス当たりのデータ転送速度は最大16Gビット/sに達する.コア当たりでは512Gビット/s(64Gバイト/s)になる.コアは16個あるので,DRAM全体では8Tビット/s(1Tバイト/s)の最大データ転送速度を達成できる.

1GビットRAMのシリコン・ダイ寸法は5.68mm×9.08mm.製造技術は45nmのCMOSを想定した.シリコン貫通電極(TSV)の材料は銅で,寸法は直径が25μm,長さが150μm,ピッチが50μm.1Tバイト/sのデータ転送に必要な消費電力は19.5Wと推定している.既存のDDR(Double Data Rate)方式のSDRAMを並べた場合,消費電力は250Wにも達するという.

写真6 DRAMのシリコン・ダイとCMOSロジック(マルチコア・プロセッサ)のシリコン・ダイをシリコン貫通電極(TSV)で接続した概念図

写真7 従来のメモリ・アーキテクチャ(上)と今回考案されたメモリ・アーキテクチャ(下)

超高速のデータ転送速度を備えたDRAMを2次キャッシュに使う.

ふくだ・あきら

テクニカルライター/アナリスト

http://d.hatena.ne.jp/affiliate_with/