次世代不揮発性メモリ技術の開発成果が続出 ―― IEDM 2009レポート

半導体デバイス技術に関する世界最大の国際学会「IEDM(International Electron Devices Meeting) 2009」が12月7日~9日に米国メリーランド州BaltimoreのHilton Baltimoreで開催された.初日の基調講演や夜のランプ・セッションなどを含めた講演セッションの数は,合計で38セッションに達する.一般講演のセッション数は35セッション.これだけのセッションをおよそ2日半で催行するという高密度なスケジュールである.最大で8本のセッションが同時に進行しており,すべてのセッションを聴講することはほぼ不可能である.そこで本レポートでは,半導体メモリ関連の発表に絞って講演概要をお届けする.

写真1 IEDM 2009の会場となったHilton Baltimore(米国メリーランド州Baltimore)

●Numonyxが1Gビットの大容量PCM技術の詳細を公表

半導体メモリ分野で研究開発が盛んなのは,次世代の不揮発性メモリ技術である.不揮発性メモリの代表であるフラッシュ・メモリは,書き換えに時間がかかる,書き換え回数に制限がある,という弱点を有する.そこで書き換え可能な回数がフラッシュ・メモリよりもはるかに多く,書き換え速度がフラッシュ・メモリよりもはるかに高い不揮発性メモリが研究されている.IEDM 2009では,その最新の研究成果が発表された.

特に目立っていたのは,米国Intel社とSTMicroelectronics社の合弁企業であり,NORフラッシュ・メモリ大手のスイスNumonyx社だ.同社は次世代不揮発性メモリの有力候補である「相変化メモリ(PCM)」を熱心に開発しており,IEDM 2009では開発成果の一部を公表した.

相変化メモリは,カルコゲナイド合金のGeSbTe(ゲルマニウム・アンチモン・テルル)が結晶状態(結晶相)とアモルファス状態(アモルファス相)の二つの状態(相)を往復できる性質を利用したメモリである.加熱と冷却の条件を変えることで,GeSbTeはどちらかの状態となる.結晶状態では電気抵抗値が低く,アモルファス状態では電気抵抗値が高い.この違いを利用してディジタル・データを記憶する.この状態は電源を切っても維持されるので,不揮発性メモリの記憶素子として利用できる.

Numonyx社は今回,1Gビットの相変化メモリを開発したことを公表した(講演番号5.7.1).相変化メモリとしては過去最大の記憶容量となる.製造技術は45nmのCMOS技術である.メモリ・セルの面積は0.015μm2(平方ミクロン)と小さい.1個の選択トランジスタと1個のGeSbTe素子でメモリ・セルを構成する.選択トランジスタに縦型バイポーラを採用することで,メモリ・セルの面積を小さく抑えた.電源電圧は1.8V.

講演では,1Gビットの試作チップの写真を発表した.試作チップの詳細は来年(2010年)2月に開催される半導体回路技術の国際学会「ISSCC(International Solid-State Circuits Conference)」で公表する予定である.2009年11月末に公表されたISSCCのアドバンス・プログラムによると,1GビットPCMチップのチップ面積は37.5mm2(平方ミリ),ランダム・アクセス時間は85ns,書き込みスループットは9Mバイト/sとなっている.

●スピン・トルクを利用した次世代デバイスについて2件の発表

次世代不揮発性メモリ技術の候補には,磁気メモリ(MRAM)もある.この分野では,スピン注入を利用したデバイスの発表が相次いだ.磁気メモリとは,強磁性体膜/トンネル絶縁膜/強磁性体膜の3層構造で,磁化方向の違いによって電気抵抗が変化する性質を利用したメモリである.2枚の強磁性体膜の磁化方向がそろっていると3層構造を貫く方向の電気抵抗が低く,強磁性体膜の磁化方向が反対向きであると電気抵抗が高くなる.磁化は電源を切っても消えないので,不揮発性メモリに応用できる.

ここでスピン注入(STT:spin-transfer-torque)とは強磁性体膜を貫く電子のスピンによって磁化の方向を変化させる技術で,高密度の磁気メモリを実現する手法として期待されている.

台湾TSMC(Taiwan Semiconductor Manufacturing Co.)社と米国Qualcomm社の共同研究チームは,CMOSロジックLSIへの埋め込みを想定したスピン注入磁気メモリ技術を開発した(講演番号11.6).製造技術は45nmのCMOSプロセス(TSMC社のLP版CMOSロジック・プロセス)である.1個の選択トランジスタと1個のスピン注入素子(強磁性体膜/トンネル絶縁膜/強磁性体膜)でメモリ・セルを構成する.選択トランジスタはMOS FETである.メモリ・セル面積は0.1026μm2.試作したメモリ・セルは,信頼性試験によって10の13乗回の書き換え寿命があると推定した.また32Mビットのメモリ・マクロと1Mビットのメモリ・マクロを試作してみせた.

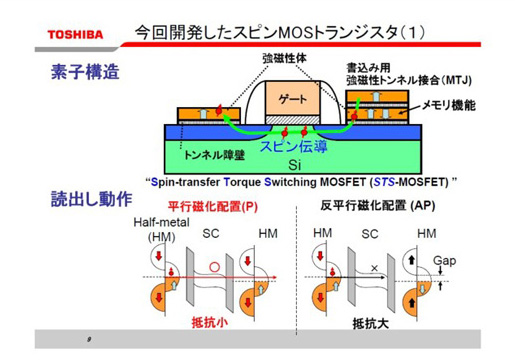

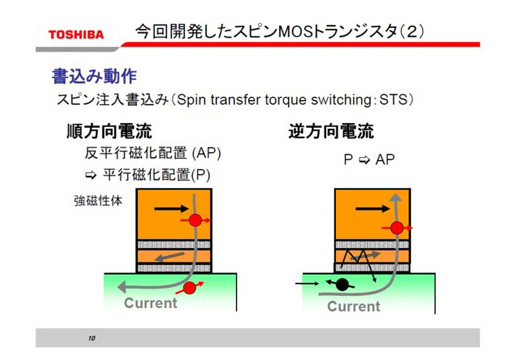

東芝は,スピン注入素子とシリコンMOSFETを一体化したデバイス(東芝は「スピンMOSトランジスタ」と呼称)を考案した(講演番号9.2).MOSFETのソースとドレインにそれぞれスピン注入素子を重ねた電極構造をしており,スピン注入素子に磁化の状態を書き込むことでMOSFETのON/OFFを制御する.ソース側とドレイン側で磁化の向きが同じ(平行配置)の場合はON状態となる.これは,電子がスピンを保存した状態でチャネルを伝搬することを意味する.現状では試作したトランジスタのON状態とOFF状態の抵抗変化はわずかなものだが,将来性は十分にある.書き込んだ磁化の状態は電源を切っても保存されるので,再構成可能な不揮発性のロジック,あるいは不揮発性メモリといった応用が考えられる.

写真2 東芝が開発したスピンMOSトランジスタの素子構造と読み出し原理

写真3 東芝が開発したスピンMOSトランジスタの書き込み原理

●抵抗変化型メモリ技術で2Mビット・チップを試作

次世代不揮発性メモリの候補にはこのほか,「抵抗変化型メモリ(ReRAM)」と呼ばれるグループがある.共通しているのは酸化物絶縁材料の抵抗変化を利用している点で,絶縁材料に加える電気パルスの条件(電圧と時間)を変えることによって高抵抗状態あるいは低抵抗状態を作り出す.

台湾のNational Tsing-Hua UniversityとTSMCの共同研究チームは,90nmのCMOSロジック・プロセスで作製できる埋め込み用抵抗変化型メモリ技術を開発した(講演番号5.6).1個の選択トランジスタと1個の抵抗素子でメモリ・セルを構成する.選択トランジスタはMOS ET,抵抗素子はタングステン(W)プラグ電極/窒化チタン(TiN)金属電極/酸化窒化チタン(TiON)絶縁層/二酸化シリコン(SiO2)絶縁層/シリコン(Si)導電層(MOS FETのソース領域)の多層構造である.試作したメモリ・セルの面積は0.1938μm2.電源電圧は4V.記憶容量が2Mビットのチップを試作してみせた.チップ寸法は0.75ミリ×0.71ミリである.

ふくだ・あきら

フリーランステクノロジーライター

http://d.hatena.ne.jp/affiliate_with/