ソフト・エラーの新要因やTSVの信頼性データなどが登場 ―― 国際信頼性物理シンポジウム(IRPS)2011レポート

半導体の信頼性物理に関する世界最大規模の国際会議「国際信頼性物理シンポジウム(IRPS:International Reliability Physics Symposium)」が4月12~14日に米国カリフォルニア州Montereyで開催された.半導体デバイスの不良を引き起こす物理現象とそのモデリング,そして対策技術に関するトピックスが議論された(写真1).

写真1 国際信頼性物理シンポジウム(IRPS)の会場風景

米国カリフォルニア州MontereyのHyatt Regency Montereyで開催された.

半導体デバイスの不良は一般に,3種類の時期に分けて論じられる.すなわち「初期不良期」,「偶発不良期」,「磨耗不良期」である.

初期不良期は半導体デバイスの製造直後に起こる不良で,時間経過とともに不良の発生率(単位時間当たりの発生確率)が下がっていく.製造工程で混入した欠陥が不良にならず,検査やテストなどをくぐり抜けて市場に出荷されてから不良として顕在化することが少なくない.テストでいかに初期不良を取り除くかが,半導体製造の重要な課題でもある.

偶発不良期は半導体デバイスの不良率が最も低い時期で,理論的にはほぼ一定の不良率を保つ.この時期に起こるとされる代表的な不良がソフト・エラーである.半導体デバイスが壊れるのではなく,半導体デバイスが一時的に誤動作してしまう不良だ.リセットしたり,電源を切って再投入したりすると,正常に動作するようになる.

磨耗不良期は半導体デバイスの寿命が尽きた時期に相当する.時間経過とともに不良率が増大し,最終的にはすべての半導体デバイスが故障する.実用的には10年の動作寿命を半導体デバイスは保証しており,磨耗不良を引き起こすさまざまな物理現象にあらかじめ対処することが求められる.磨耗不良を引き起こす物理現象には,TDDB(Time Dependent Dielectric Breakdown;絶縁膜の経時破壊),エレクトロマイグレーション,ホットキャリア,NBTI(Negative Bias Temperature Instability;負バイアス温度不安定性)などがある.

●宇宙線に含まれる素粒子がソフト・エラーを引き起こす

それでは「国際信頼性物理シンポジウム(IRPS)」のトピックスを紹介していこう.

ソフト・エラーでは最近は,中性子線を原因とするソフト・エラーの研究が盛んである.宇宙線が地球の大気と衝突して中性子線が発生し,地上に降り注ぐ.中性子線がまれに半導体デバイスのシリコン原子核と衝突し,2次イオンの粒子(2次イオン線)をまき散らす.2次イオン線の電荷がロジック回路の電位を変動させたり,メモリ回路の電位を反転させたりする.

これに対して宇宙線の一部であるミューオン(ミュー粒子)がソフト・エラーの原因となることを,米国のVanderbilt UniversityとCisco Systems社,Marvell Semiconductor社,Texas Instruments社の共同研究チームが明らかにした(B.D.Sierawskiほか,講演番号3C.3).ミューオンは素粒子の一種で,電子と同じマイナスの電荷を有する.中性子線は電荷を持たないので,シリコン半導体の原子核と衝突しない限り,ソフト・エラーの原因とはならない.これに対してミューオンは電荷を有するので,シリコン半導体を通過するだけでソフト・エラーを引き起こすことがある.

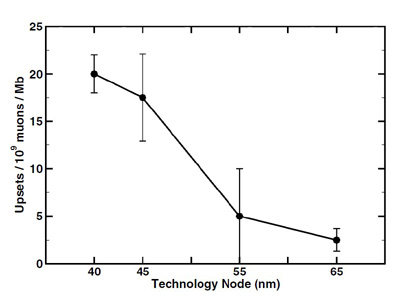

Vanderbilt Universityを中心とする共同研究チームは,最小加工寸法の異なるCMOS SRAMチップでソフト・エラーの起こりやすさを調べ,微細化とともにソフト・エラーの発生確率が増大することを実験で示した(図1).

図1 半導体製造技術の最小加工寸法とミューオンによるソフト・エラー発生率(SRAMの1Mビット当たり)の関係

●シリコン貫通ビア(TSV)の信頼性について解析

実装技術関連では,シリコン・ダイの高密度積層技術である「シリコン貫通ビア(TSV:Through Silicon Via)」の信頼性に関する講演が相次いだ.

TSVとは,金属〔通常は銅(Cu)〕の細長い柱をシリコン基板に貫通させ,積層したシリコン・ダイ同士を電気的に接続する技術である.既存技術であるワイヤ・ボンディング技術やフリップチップ技術と比べると,TSVは接続密度が高い.数多くのシリコン・ダイをTSV技術によって接続することで,超大容量メモリや大規模高密度モジュールなどを実現できると期待されている.

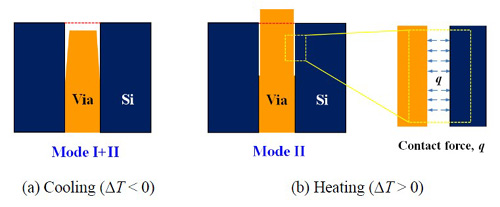

米国University of Texas at Austinは,温度サイクルによってTSVのCu柱と周囲のシリコン(Si)の間でどのような歪みが生じるのかを3次元的に解析した(K-H Luほか,講演番号3D.1).CuとSiは,熱膨張係数が異なる.温度変化があると,熱膨張係数の違いによって歪みが生じる.Si中のキャリアの移動度が低下したり,Cu柱と周囲のSiの間ではく離が起こったりする(図2).この様子を,有限要素法による3次元解析で明らかにした.

図2 温度変化によってTSVの柱と周囲のシリコンの間で応力が発生する様子

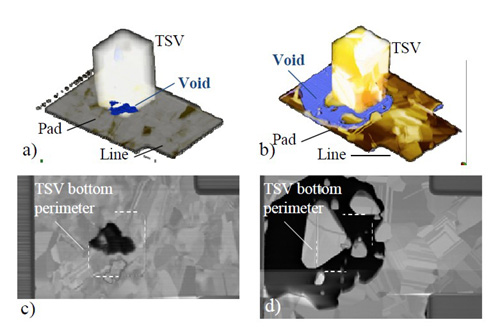

STMicroelectronics社とCEA-Leti(フランス原子力庁 電子・情報技術研究所),TIMA(Techniques of Informatics and Microelectronics for Computer Architecture)の共同研究チームは,多層金属配線のエレクトロマイグレーションがTSV直下で空孔(ボイド)を発生させる現象を発表した(T.Frankほか,講演番号3F.4).エレクトロマイグレーションとは,電流によって配線や電極などの金属原子が徐々に移動する現象を指す.エレクトロマイグレーションが進行すると配線抵抗が増大したり,あるいは逆に隣接する配線が短絡したりすることがある.

STMicroelectronics社らの共同研究チームは,Cu配線,窒化チタン(TiN)バリヤ,Cu柱の構造を試作し,Cu柱直下のCu配線にエレクトロマイグレーションによるボイドが発生することを確かめた(図3).ボイドがある程度拡大するとTSVの抵抗増大が始まり,抵抗値が徐々に増加していく.対策としては,TSVの断面積を拡大する,TSVの本数を増やす,といった手法が考えられるとしている.

図3 TSV直下に空孔(ボイド)が発生した様子

●NBTIの劣化と回復を説明するモデルを発表

NBTI関連では,劣化と回復を説明するモデルが発表された.NBTIは,高温下で負電圧バイアスしたpチャネルMOSFETの特性が不安定になる不良で,磨耗不良期に発生する不良として知られている.ただし,NBTIを引き起こすメカニズムについてはよく分かっておらず,不良モードをうまく説明できるモデルがなかった.正確なモデルが存在しないことは寿命予測が正確にはできないということを意味しており,長く懸案事項となっていた.

今回のIRPSでインドのIndian Institute of Technology Bombayと米国Purdue University,米国University of Illinois の共同研究チームは,NBTIの劣化と回復を説明するモデルを提唱した(S.Mahapatraほか,講演番号6A.3).NBTIでは負電圧バイアスを加えるとpチャネルMOSFETの特性が劣化し,負電圧バイアスを切るとpチャネルMOSFETの特性が回復する.従来は反応拡散モデル(Reaction Diffusion Model)で劣化現象を説明していたのだが,回復現象をうまく説明できなかった.Indian Institute of Technology Bombayを中心とする共同研究チームは,反応拡散モデルで劣化と回復の両方を説明できることを示し,寿命を予測してみせた.

ふくだ・あきら

フリーランステクノロジーライター

http://d.hatena.ne.jp/affiliate_with/