USB 3.0規格のFAQ(2) ―― SuperSpeed USBはいかにして高速伝送を実現しているのか?

Q.品質を落とさずに信号を高速伝送するため,どのような技術を採用しているのか?

A.デエンファシスとレシーバ・イコライザを利用している.

マルチギガ・ビット・レートの信号を基板やケーブルを通して伝送する場合の問題点として,高周波損失の顕在化があります.高周波損失の主要因は,抵抗損と誘電損の二つです.

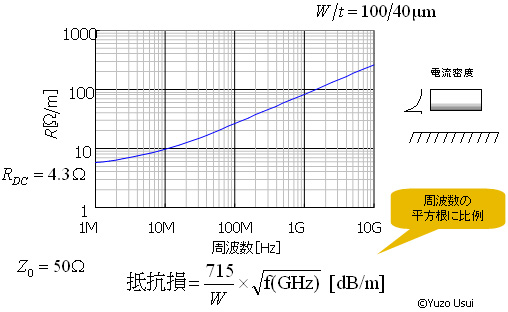

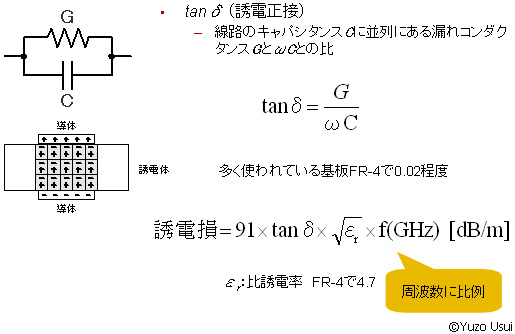

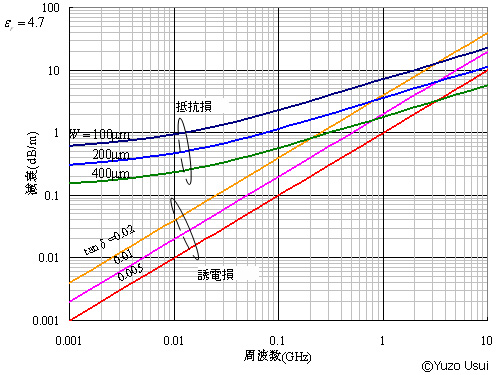

抵抗損(図4)は,交流電流が導体内部を流れなくなる(いわゆる表皮効果)ことによる損失で,周波数に比例して増加します.誘電損(図5)は,誘電体に電界をかけたときに誘電体内部で分極が発生し,周波数の上昇に伴って電界の変化と分極の変化にずれが生じて発生する損失です.周波数の平方根に比例して増加するため,周波数が低いところでは影響は小さいのですが,周波数が上昇するにつれて顕在化します.つまり,周波数の上昇に伴って減衰が増加し,伝送路があたかもローパス・フィルタであるかのように作用します(図6).

図4 ボード・パターンの抵抗損(表皮抵抗,導体損失)

図5 誘電損(誘電損失)

図6 ボードの損失(周波数に依存した減衰特性となる)

'0'や'1'の周期が短いほど高い周波数成分を持つことになり,伝送路の高周波損失の影響を大きく受けます.同時に,パターンによりエッジ位置が時間軸方向に揺らぐ現象が発生します.

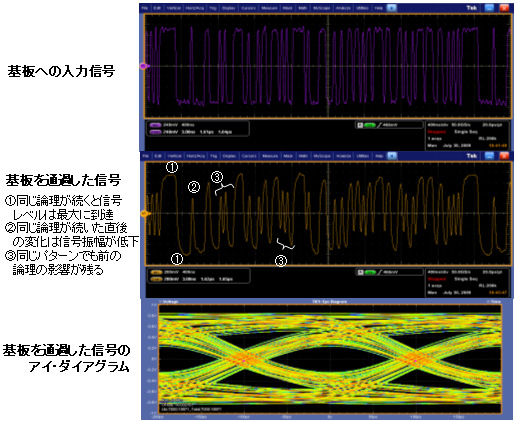

これらは前のデータ・パターンによって影響の受け方が変わり,シンボル間干渉(ISI:Inter Symbol Interference)と呼ばれています.伝送路の損失の影響を,実際の波形とアイ・ダイアグラムで見たのが図7です.シンボル間干渉が起きていることが分かります.

図7 伝送路の損失の影響を受けた波形

ここでは5Gbpsの信号をUSB 3.0の3mケーブルにて伝送しました.パターンとしては,7ビットの線形フィードバック・シフト・レジスタ(LFSR:Linear Feedback Shift Register)を使用して生成したPRBS7(Pseudo Random Bit Sequence;疑似ランダム・パターン)を使いました.なお,USB 3.0では8b/10b符号化により,同じビットの連続が最高でも5ビットまでとなります.周波数成分の広がりが7ビット同じビットが連続するPRBS7より抑制されるので,実際の影響の受け具合いはもう少し軽減されます.

信号の'0'→'1','1'→'0'というビット変化部分(遷移ビット)は,高い周波数成分を持ちます.そこで,'0'→'0','1'→'1'というように同じビットが連続(非遷移)した場合,送信側で信号レベルを下げることで相対的に遷移ビットを強調する技術をデエンファシスと呼びます.この方法により,受信端に到来した遷移ビットと非遷移ビットのレベル差をなくし,シンボル間干渉を抑制できます.

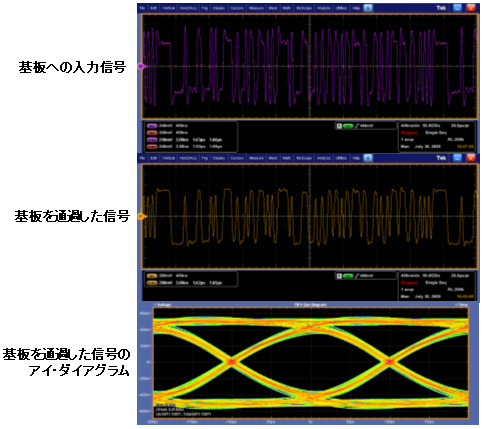

図8は,図7と同じ条件・信号に対して3.5dBのデエンファシスを適用した例です.受信した信号の品質が改善されていることは,受信波形の変動具合いが低減していることや,図7と比べてアイ・ダイアグラムが大幅に開いていることから判断できます.

図8 デエンファシスを適用して改善を図った例

余談ですが,デエンファシスというと通信の世界では,送信時の変調前に強調(プリエンファシス)した周波数成分を,受信側で復調後に元に戻すことをいいます.実際にFM放送の送受信に取り入れられています.これに対して,最近のシリアル・インターフェースでは,プリエンファシスは遷移ビットを強めることを,デエンファシスは逆に非遷移ビットのレベルを下げることを意味しています.

実際のUSB 3.0の信号を見てみましょう.図9はホスト・アダプタ・カード(NECエレクトロニクス製)のレセプタクル直後の波形です.すでに基板トレースの減衰の影響を受けているためやや不明瞭ですが,遷移ビットと非遷移ビットの振幅が異なっています.なお,後述の規格(参考仕様)はチップのパッドで規定されています.

図9 ホスト・コントローラ・カードに見るデエンファシス

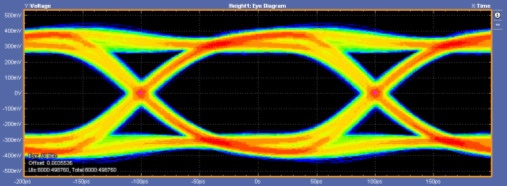

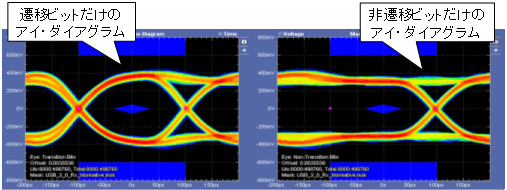

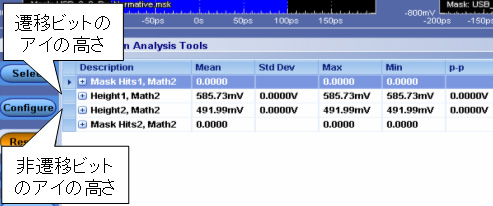

図10では,図9の信号の遷移ビットと非遷移ビットを分離し,それぞれのアイの高さを測定してみました.左側(遷移ビット)のアイの高さはHeight1として585.73mV,右側(非遷移ビット)のアイの高さはHeight2として471.99mVと測定されています.遷移ビットのアイの高さのほうが大きくなっていることが分かります.

USB 3.0と同じ5Gbps伝送のPCI Express Rev. 2.0では,5Gbpsで6dB,および3.5dBというデエンファシスを規格化しています.前者については遷移ビットに対して非遷移ビットの信号レベルを1/2に,後者は2/3に下げることになります.6dB下げるということは,USB 3.0の想定する伝送路ではレシーバ感度が厳しくなります.反対に信号振幅を上げる方法も考えられますが,消費電力やEMI(電磁輻射ノイズ)の増加を招きます.そのため,USB 3.0では送信側のデエンファシスを3.5dB(±0.5dB)に抑え,さらに不足分の補正を受信側のイコライザで施す方法(Receiver Equalization)を採用しています.

(a) アイ・ダイアグラム

(b) アイの高さの測定結果

図10 遷移ビットと非遷移ビットを分離

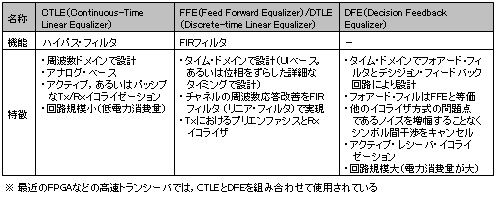

表1はイコライザの種類です.USB 3.0ではどのイコライザを使うかという規定はありません.ただしトランスミッタは,リンクアップ(Polling)中に伝送路の減衰特性に合わせてイコライザを最適化するためのパターン(TSEQ)を送信するようになっています.

表1 イコライザの種類