初めてでも使えるVerilog HDL文法ガイド ―― 記述スタイル編

tag: 半導体 ディジタル・デザイン

技術解説 2009年7月10日

4.テストベンチ向き構文

設計した回路を効率的に検証するために,Verilog HDLの記述能力を最大限利用することができます.テストベンチは,ある意味で「プログラミング」です.プログラミングに必要な構文が,Verilog HDLには多数用意されています.

● サブルーチンに相当する「タスク」

テスト入力の作成や,期待値との照合にサブルーチンに相当する概念のタスクを用いると,検証効率を向上できます.

タスクはサブルーチンの一種ですから,タスクの定義やタスクの呼び出しがあります.また,呼び出し側とのデータの受け渡しを行う「引き数」もあります.さらに,タスクの中で別のタスクを呼び出す「ネスティング」も可能です.

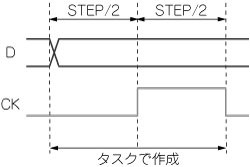

リスト9のテストベンチを,タスクを用いて記述し直してみました.図6のように,クロック1周期分の期間でD入力とクロックCKを制御し,フリップフロップへ任意の値を書き込むタスクを記述してみました(リスト10).

図6 入力波形

対象の一つ上の階層でテストベンチを作成する.ここで入力を与えて出力を観測するしくみを作る.

リスト10 タスクを用いたテストベンチ

タスクは,taskに続いてタスク名と引き数の宣言を記述します.この例では引き数が入力(input)ですが,出力の引き数(output)も可能です.

タスクをサブルーチンとすれば,モジュール内で宣言した信号はグローバル信号です.したがって,モジュール内で宣言した信号をタスク内で参照できます.ここでは,テスト対象に接続しているDやCKに対し,タスク内から値を設定しています.D入力に対して,引き数のdataを代入しています.

タスク内では遅延も記述できます.ここではSTEP/2単位で信号を変化させ,図6の入力を実現しています.

タスクは,システム・タスクと同じようにinitial内で呼び出します.リスト10に示すようにタスクの呼び出しを記述します.ここでは4ビットの定数を連続的に4ビット・フリップフロップに書き込んでいます.

このタスクでは,シミュレーション開始直後からSTEP/2ユニット後にCKの値が確定します.それ以前は不定値です.これを防ぐため,CKの宣言時に'0'を初期値として与えています.変数宣言時の初期値設定はとても便利ですが,回路記述内で使うことは禁止です.多くの場合,論理合成ツールで無視されます.レジスタ類の初期化はリセット機能としてきちんと記述する必要があります.

● ループ構文など

ループを作る構文には,for文,while文,repeat文,forever文などがあります.また,強制代入のforce文やforce文の解除のrelease文など,さまざまな構文があります.

● システム・タスク

シミュレーション結果を表示したりファイルに出力するため,さまざまなシステム・タスクが用意されています.とくに,ファイルの入出力については,C言語と同様の名称と機能があります.

● コンパイラ指示子

module~endmoduleの外部に記述でき,記述のコンパイル時に作用するさまざまな構文があります.バック・クォート(`)で始まるこれらの構文を「コンパイラ指示子」と呼びます.

`define テキスト・マクロ

`timescale シミュレーション時間の単位づけ

`include ファイル読み込み

`ifdef,`else,`endif,`elsif 条件コンパイル

などがあります.

こばやし・まさる