初めてでも使えるVerilog HDL文法ガイド ―― 記述スタイル編

tag: 半導体 ディジタル・デザイン

技術解説 2009年7月10日

2.5 下位モジュール接続

別途定義したモジュールを,上位階層で接続することもできます.機能的にまとまった単位でモジュール化し,これらを接続して一つの階層を作り,さらにこれらを上位階層で接続して...というような階層設計が可能です.

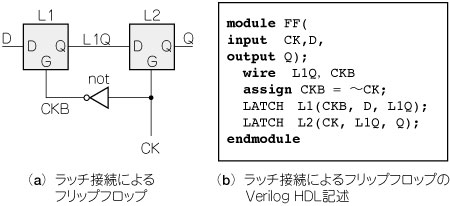

図3では,リスト4のラッチを二つ接続してフリップフロップを作成しています.内部で使用する二つの信号L1QとCKBは値を保持しないので,ネット型(wire)で宣言しています.

図3 フリップフロップ回路

ここで示したフリップフロップは,モジュール接続の例として出した.実際のフリップフロップは,リスト7に示したようにalwaysを使って記述する.

下位モジュールの接続は次のように行います.接続するモジュール名に続き,インスタンス名(この場合はL1,L2)を記述します.さらにかっこ内に接続する信号をコンマで区切って並べます.記述順にモジュール定義側と接続されます.順番をまちがえると,正しく接続されません.

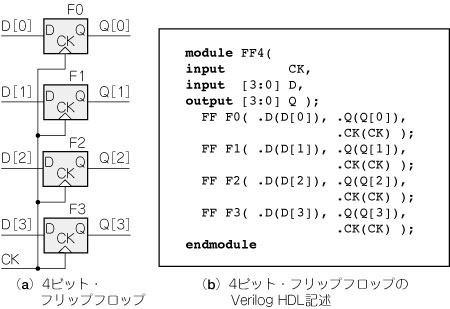

図4はこのフリップフロップを4個接続して4ビット・フリップフロップを構成したものです.ここでは入出力に名まえによる接続を行っています.

.定義側ポート名(接続信号名)

とすることで順番が任意になります.モジュール接続時にポート数が数十になることも珍しくないので,順番が任意であることは有用です.ただし,順番による接続と名まえによる接続は混在できません.

図4 4ビット・フリップフロップ

名まえによる接続は順番に依存しないので,誤りの入る余地が少ない.確実な設計を目指すのならこれを使うべきだが,記述の手間がかかるのが難である.Perlスクリプトなどを使ってポート・リストを自動生成する簡易ツールを作った例をもあるようだ.

2.6 そのほかのRTL記述

● generateによる回路の切り換え

図3のフリップフロップの記述は確かに動作しますが,現実的ではありません.フリップフロップには適した記述があり,通常alwaysを使います.これら2種類の記述をgenerateとif文を用いて切り換えてみました(リスト7).

リスト7 generateとif文

generate~endgenerate内にif~elseの構造で2種類のフリップフロップを記述し,パラメータ宣言した定数ff_typeによって切り換えています.generate内には回路記述で使う大半の構文を記述できます.ポートやモジュール内で宣言した信号にアクセスできるので,CKやD入力を参照し,出力Qに信号を与えています.

parameterは定数なので,このままではつねにラッチ接続のフリップフロップになってしまいますが,上位階層でこのモジュールを接続するときに,

FF #(.ff_type(1)) F1(CK, D, Q);

とすることで,ff_typeに値を与えることができます.parameterはデフォルト値として扱われます.

● generateによる回路の繰り返し

generate内にはfor文を記述できるので,これを利用することで回路を繰り返し接続できます.リスト8は,図4をgenerateを使って書き換えたものです.generate内部にローカルな変数iをgenvarを使って宣言し,for文のループ変数にしています.これを接続する多ビット信号のビット選択に使っています.

リスト8 generateとfor 文

この記述では,ビット幅をパラメータ宣言を使って定義しました.前の例と同じように,このモジュールを上位階層で接続するときに任意のビット幅にすることができます.パラメータ宣言は,ポート・リストのかっこ内に位置できないので,今までと異なったスタイルでポートを宣言しています.モジュール名に続き,かっこ内でポート名だけをリストし,モジュール内でポートの方向やビット幅を定義しています.